Hi,

There is a confusion with AM3505 Power-up sequencing from the datasheet and reference documents.

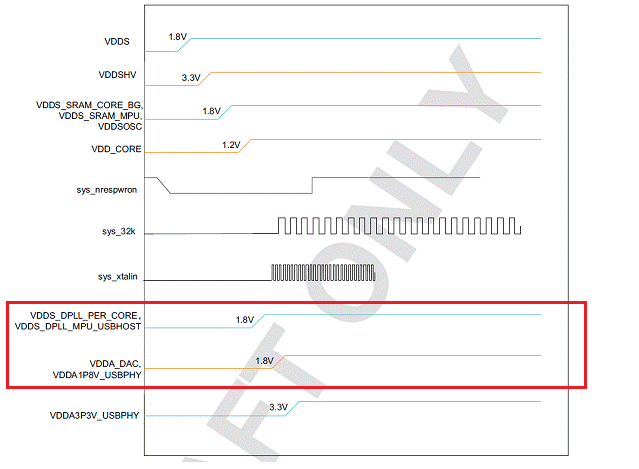

As per the latest datasheet, the VDDS_DPLL_xx and VDDA1P8V_USBPHY could be ramped up at the same time.

But as per the power reference design and the wiki Design In Guide,

it is mentioned that VDDA1P8V_USBPHY should be ramped after VDDS_DPLL_xx.

http://www.ti.com/analog/docs/refdesignovw.tsp?familyId=64&contentType=2&genContentId=68614

http://processors.wiki.ti.com/index.php/AM35x_with_TPS65023:_Design_In_Guide#1.8V_Operation_Sequence

Could you please let us know which one is correct,

can we assume the latest datasheet is the proper one and it is ok to ramp-up simultaneous

and can we use the same 1.8V power source for both VDDS_DPLL_xx and VDDA1P8V_USBPHY?

The wiki has a statement saying

"It is recommended that you combine the voltage source for VDDS_DPLL_MPU_USBHOST and VDDS_DPLL_PER_CORE,

but that source should not power other 1.8V supplies (ie, 1.8V for USB or VDAC) "

http://processors.wiki.ti.com/index.php/AM35x_with_TPS65023:_Design_In_Guide#USB_voltage

Best Regards

Kummi

-

Ask a related question

What is a related question?A related question is a question created from another question. When the related question is created, it will be automatically linked to the original question.