Other Parts Discussed in Thread: TCI6638K2K, TCI6636K2H

In this case, I want to archieve debug DSP part thrugh CCS of IPC examples. According to the MCSDK's System Management,

by default, the DSP cores are powered down by u-boot at the time of EVM boot. After kernel is running, MPM can be used to load

and run DSP images from linux command-line/utility. Rather than using MPM, if you want to use CCS to load and run DSP images,

then set the following setting in u-boot prompt:

setenv debug_options 1 saveenv reset

However, it does not work. There are two pictures caughted in my opration.

1.the u-boot environment

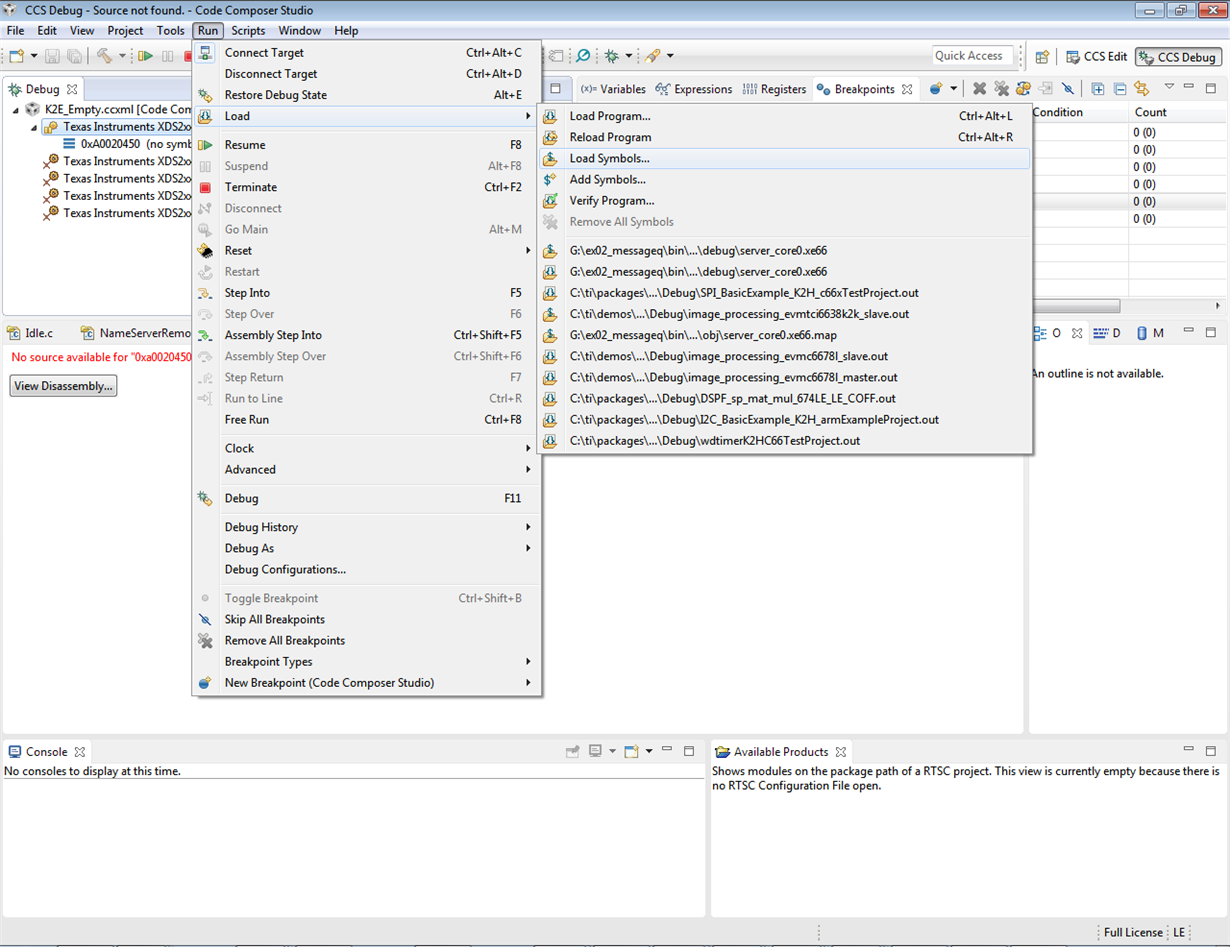

2.debug my dsp binary program through CCS

-------------------------------------------------------------------------------------------------------------------------------------------------------------------

Platform: EVMK2H

PDK version: ti-processor-sdk-linux-k2hk-evm-02.00.02.11 && ti-processor-sdk-rtos-k2hk-evm-02.00.02.11

Filesystem version: using the image from ti-processor-sdk-linux-k2hk-evm-02.00.02.11

Examples I'm running : IPC3.42XX/examples/TCI6636_linux_elf/ex02_messageq

----------------------------------------------------------

Xiaop