Hi,

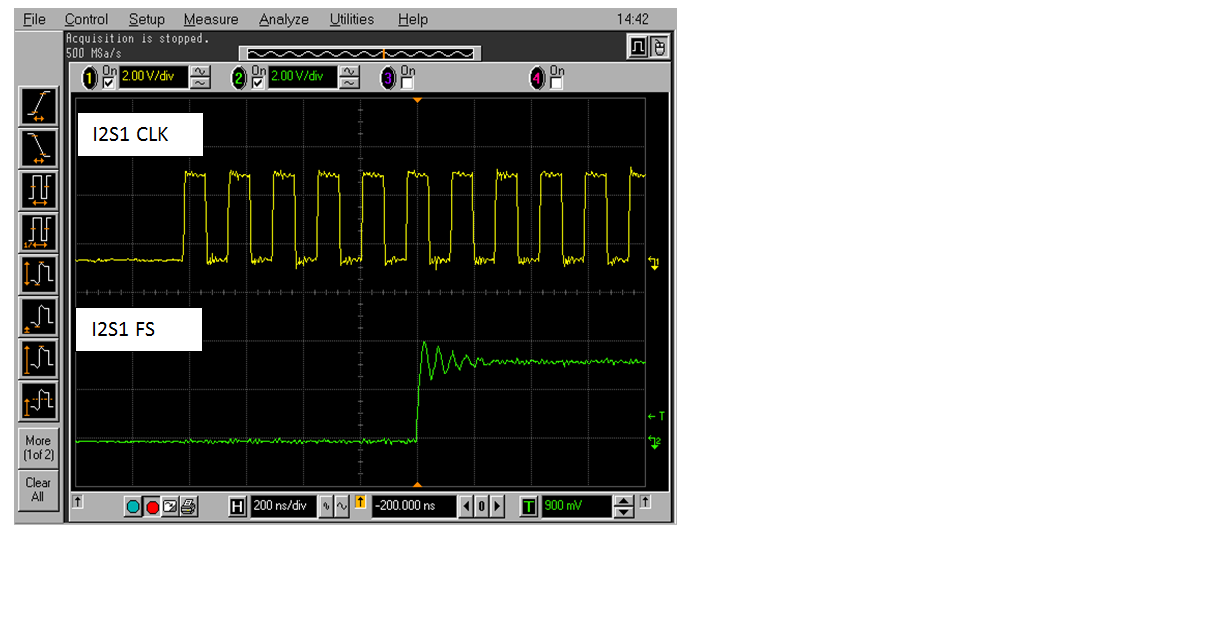

My customer is now facing the problem with losing I2S data on receive buffer at the begging of I2S frame.

First of all, please take a look at the attached spread sheet. I've tried to explain the phenomenon.

They are in trouble with this issue and need to fix this issue soon.

So could you please explain the mechanism for this issue and let us know the related descriptions in the manual you provided.

Also, please review the register configurations (see attached) and let me know if you have any suspicion for this issue.

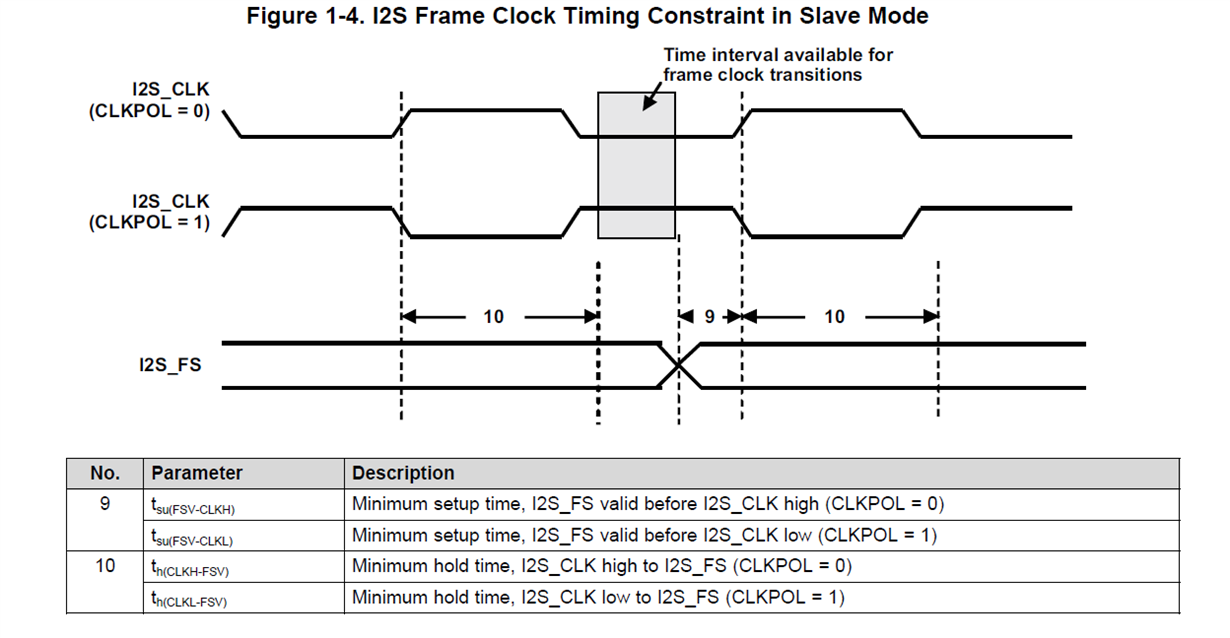

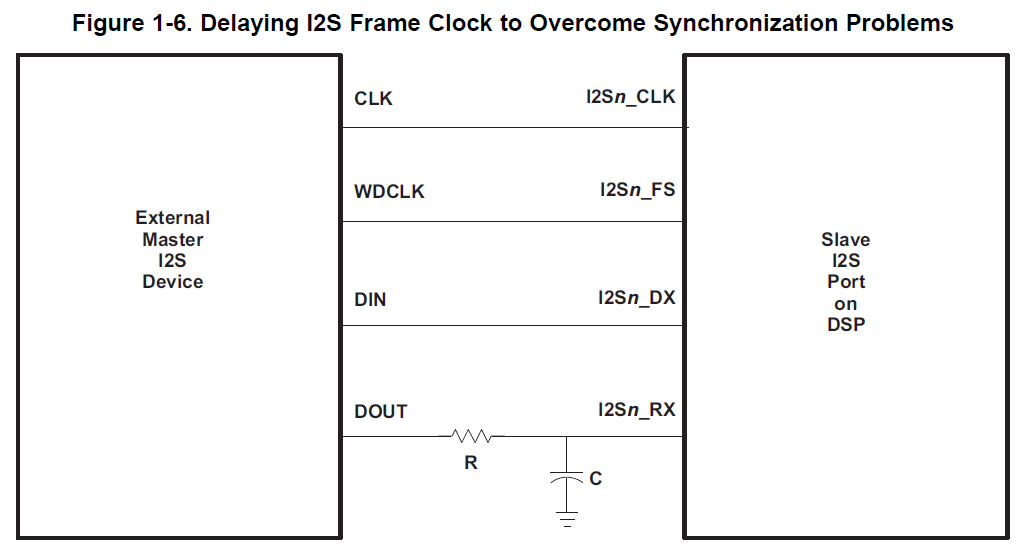

To me, the register values looks correct and this issue looks I2S clocking issue, I mean some clocks have to be fed to I2S to 'activate' its receive block at the first/beginning of frame sync. This is described in TRM:

But as you see in the spread sheet, they are actually loosing 5 frames, not 3. so we need more detailed/additional information for this behavior if the issue is related to this restriction.

Also, the errata might be related to this issue. Please find the following:

www.tij.co.jp/.../sprz308d.pdf

Advisory 2.0.4 I2S: I2S Internal Data Delay

It says 3 zero words reception would be expected at first 3 frames.

But actually DSP does not match this restriction....Also some information is available on Table 6. Feedback Path Internal Data Delays, but in fact, I can't understand what is meant by this table. Could you please explain ?

Anyway, please check the attached spread sheet carefully. I've summarized the issue in detail.

Sorry to have troubled you, but It would be so appreciated if you could reply soon!

Best Regards,

Naoki