Hi,Everyone,

I use C6678EVM ,pcie boot ,and I have some questions as following :

After I use linux PC transport the image of project to DDR,and linux PC would write boot entry address to core 0's magic address ,and core 0 can run as well.

Then core 0 will write the entry address to core 1.....7's magic address ,the code I use as following :

if(DNUM==0)

{

for (core = 1; core < 8; core++)

{

if(DEVICE_REG32_R(BOOT_MAGIC_ADDR(core))==0)

{

DEVICE_REG32_W(BOOT_MAGIC_ADDR(core), (uint32_t)&_c_int00);

}

}

}

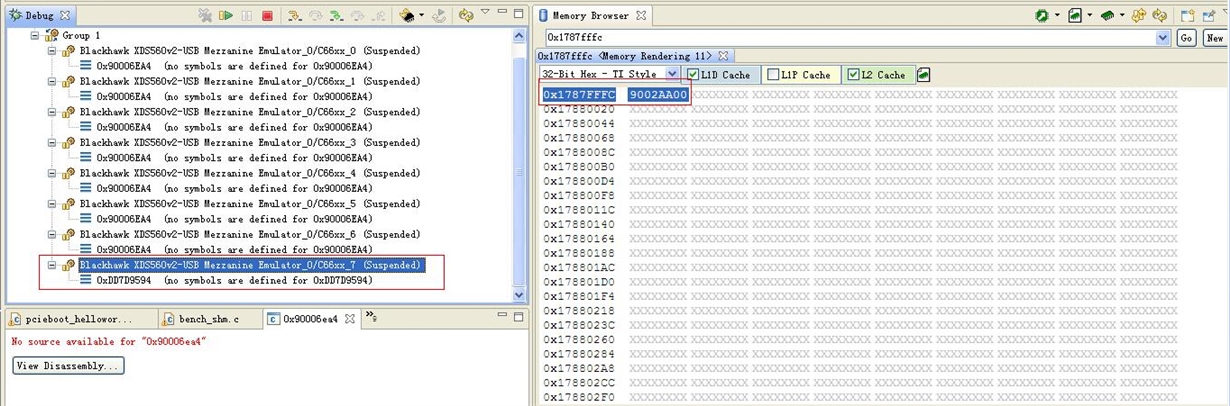

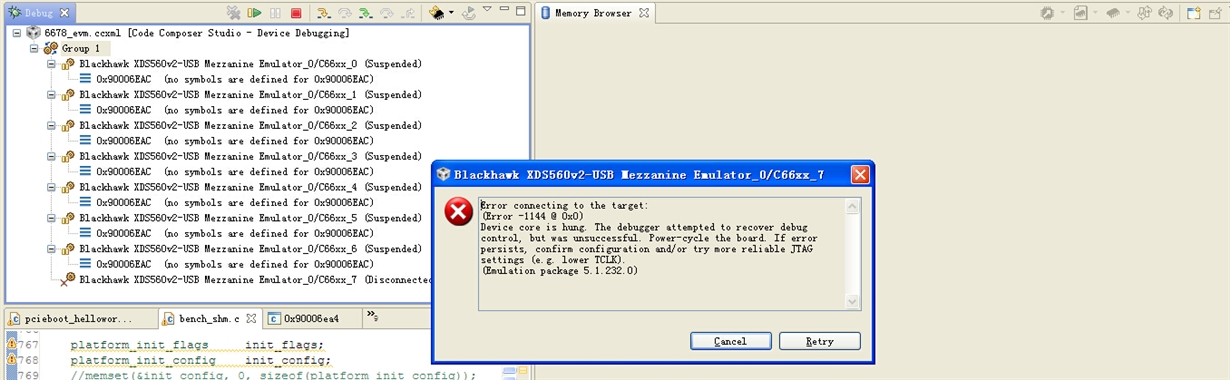

And core 1....6 can run as well after core 0 execute above code ,but core 7 can't ,I have checked it after connect CCS,you can see the picture as following :

core 7 isn't execute the code in the value of magic address (boot entry address 0x9002AA00),why ?

Regards,

Simon