My team found that the use of AB18/AE18 for I2C1 (select from Pin Mux Tool) could only generate the 1st byte (slave address) with ACK (Low) from Device, no further clock and data for conmunication.

When we reworked to use G20/E25 for I2C1, the same configuration (OS,Driver,etc) resulted the I2C device read/write passed.

My team want to know whether AB18/AE18 could be configured as normal I2C Bus (I2C1) or any special cofiguration is required.

Arc Chen

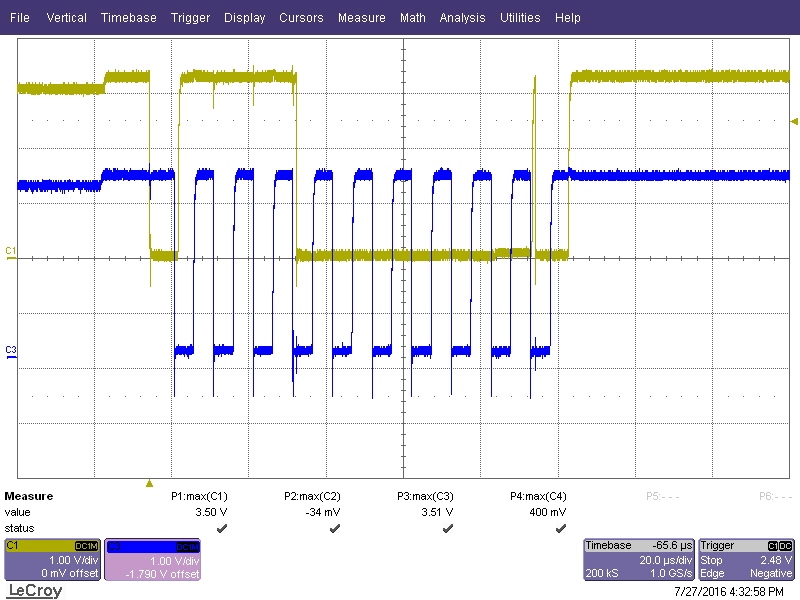

I2C1 (SCL/AB18, SDA/AE18) waveform with only 1st byte: