Hello!

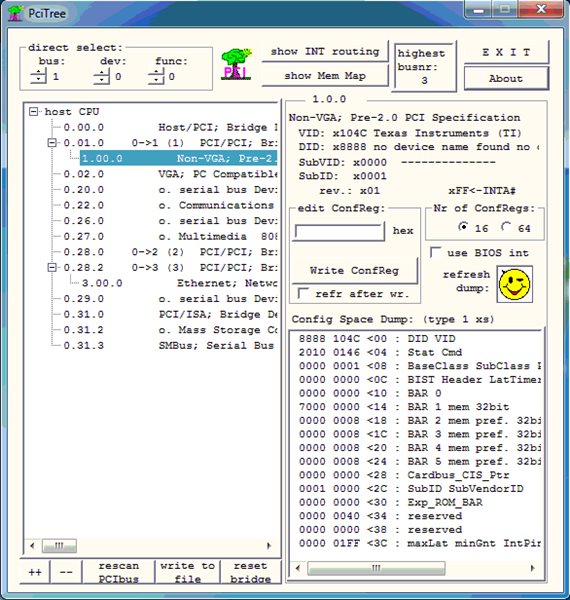

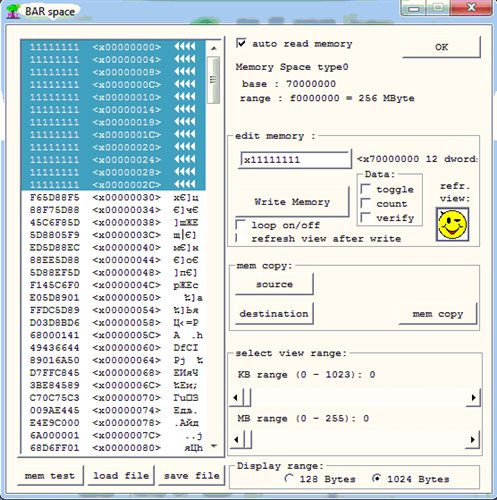

I'm trying to run PCIE_evmc6678_wSoCFile_C66BiosExampleProject on my evm6678le board inserted in PC. Program goes in bebug mode to moment of waiting receiving data from RC and receives nothing (I evaluate dstBuf variable, there are all elements null). I have no RC board and that is why I'm writing to 0x70000000 PCIe base address of EP evm6678le board 1 K of data (all words were 0x11111111) by software on PC(PCITree) but I can't see that data recieves in dstBuf variable . Also I've modified Example program on evm6678 and I've scanned range 0x00000000 - 0xFFFFFFFF of internal board adresses for my data (0x11111111) and it shows that there are no such data in board memory. Why can't I receive anything?

Also, can you advise me about scanning function if I've wrote something wrong in it?

unsigned int* t_adr = 0x00000000;

do {

if(*t_adr == 0x11111111){

PCIE_logPrintf (" address = 0x%08x \n", t_adr);

PCIE_logPrintf (" data = 0x%08x \n", *t_adr);

t_adr++;

}else{

t_adr++;

}

} while (true);