Hi,

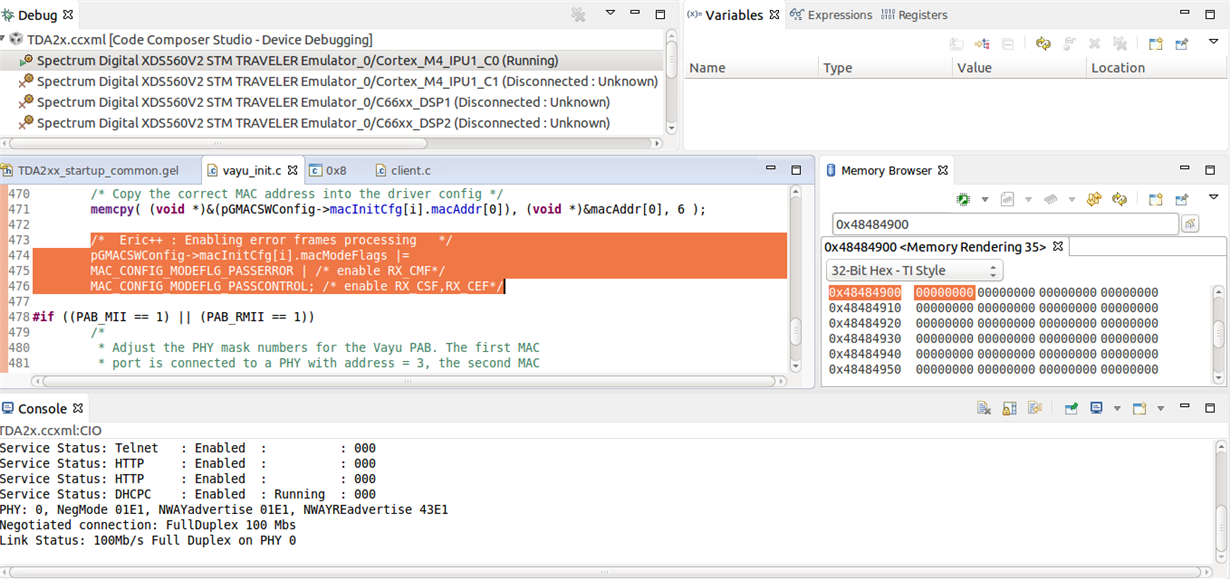

For Tda2x EVM, it used Gig Phyter (DP83865 Gig PHYTER V10/100/1000 Ethernet Physical Layer) and Vision SDK was set to RGMII mode for Ethernet.

Our EVM use Mig Phyter (DP83848Q-Q1 PHYTERTM Extended-Temperature, Single-Port 10/100-Mbps Ethernet Physical Layer Transceiver) for Ethernet.

So I must configure Ethernet MAC interface to MII mode in Vision SDK.

I list my modification as follow:

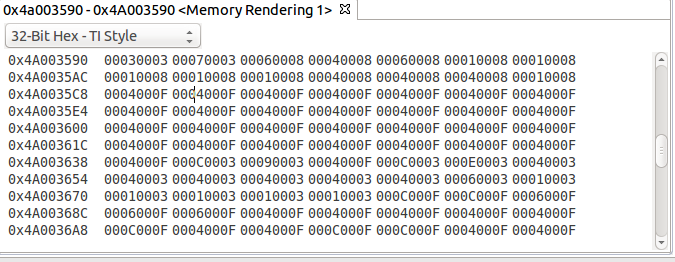

1. according to HW schematics, I modified some pin mux setting in file

VISION_SDK_02_10_00_00/ti_components/drivers/starterware_01_06_00_16/bootloader/sbl_utils/src/sbl_utils_tda2xx.c

Phy Pin name ball Pad Name Offset Register Value

MDC EPHY_MDC O D3 VIN2A_D10 0x190 0x4000F

MDIO EPHY_MDIO I/O F6 VIN2A_D11 0x194 0x4000F

RXD_1 EPHY_RXD I V6 RGMII0_TXD1 0x260 0x40003

RXD_2 EPHY_RXD I V9 RGMII0_TXCTL 0x254 0x40003

RXD_3 EPHY_RXD I W9 RGMII0_TXC 0x250 0x40003

RXD_0 EPHY_RXD I U6 RGMII0_TXD0 0x264 0x40003

RX_CLK EPHY_RXC I Y1 UART3_TXD 0x24C 0xE0003

RX_DV EPHY_RXDV I V2 UART3_RXD 0x248 0xC0003

TX_CLK EPHY_TXC I U5 RGMII0_RXC 0x268 0x60003

TXD_0 EPHY_TXD O W2 RGMII0_RXD0 0x27C 0x10003

TXD_1 EPHY_TXD O Y2 RGMII0_RXD1 0x278 0x10003

TXD_2 EPHY_TXD O V4 RGMII0_RXD3 0x270 0x10003

TXD_3 EPHY_TXD O V5 RGMII0_RXCTL 0x26C 0x10003

TX_ER EPHY_TXER I U4 MDIO_D 0x240 0x90003

RX_ER EPHY_RXER I U7 RGMII0_TXD2 0x25C 0x40003

COL EPHY_COL I V1 MDIO_MCLK 0x23C 0xC0003

CRS EPHY_CRS I V7 RGMII0_TXD3 0x258 0x40003

TX_EN EPHY_TXEN O V3 RGMII0_RXD2 0x274 0x10003

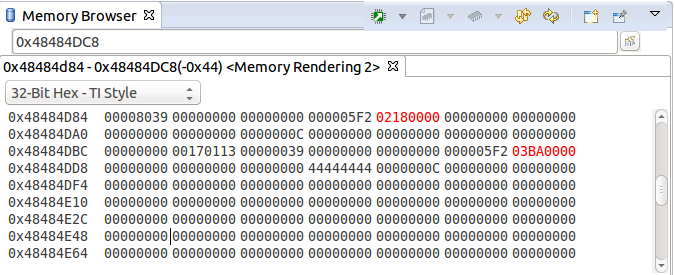

2. Remove this function. If not, system will restore to RGMII configure after booting.

VISION_SDK_02_10_00_00/ti_components/drivers/starterware_01_06_00_16/platform/platform_tda2xx_pad_config.c

void PlatformRGMIISetPinMux(void)

{

// PlatformRGMII0SetPinMux();

}

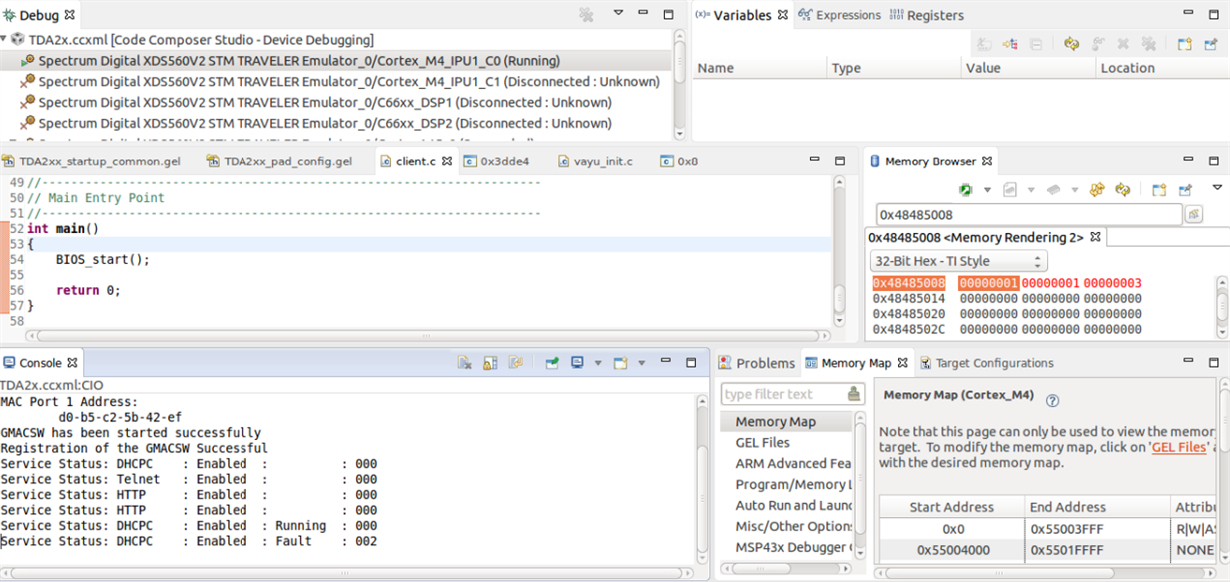

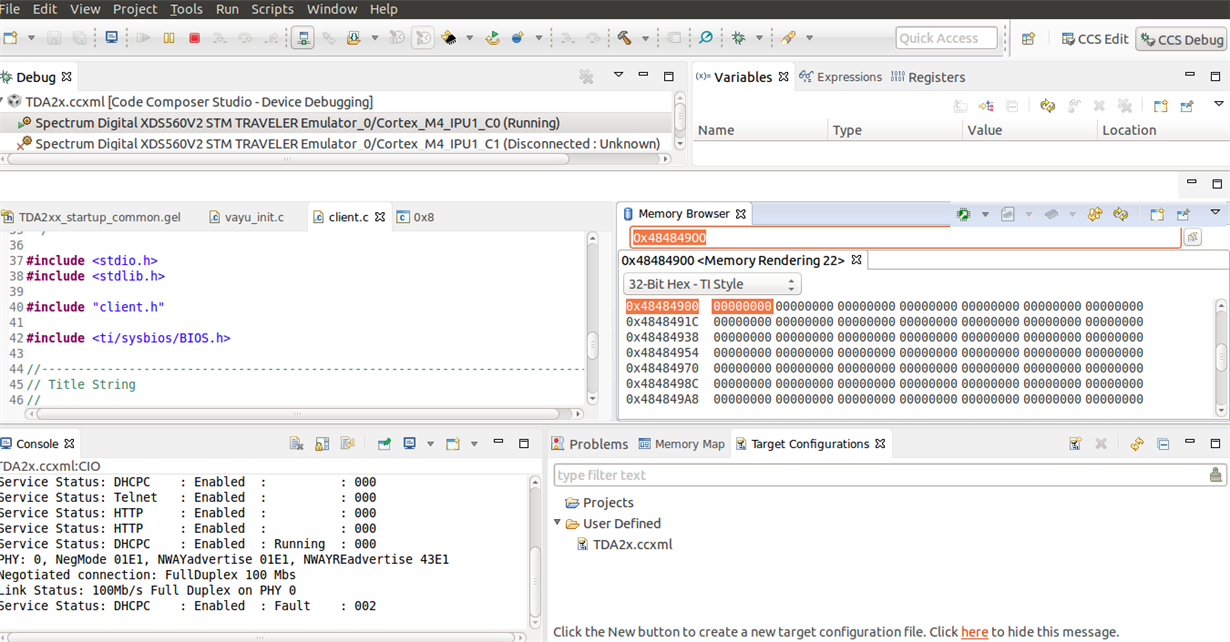

After Booting, system still can't get IP from DHCP server.

Are there any settings I need to do more?