Hi,

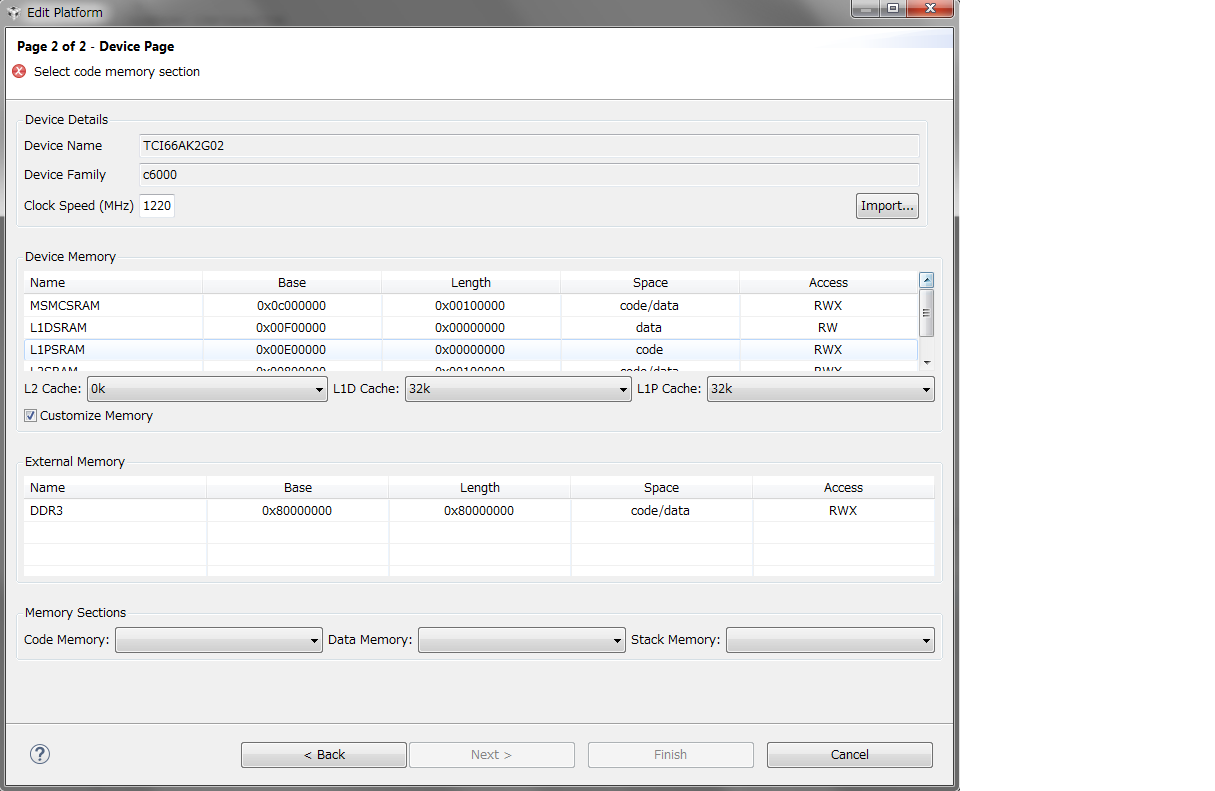

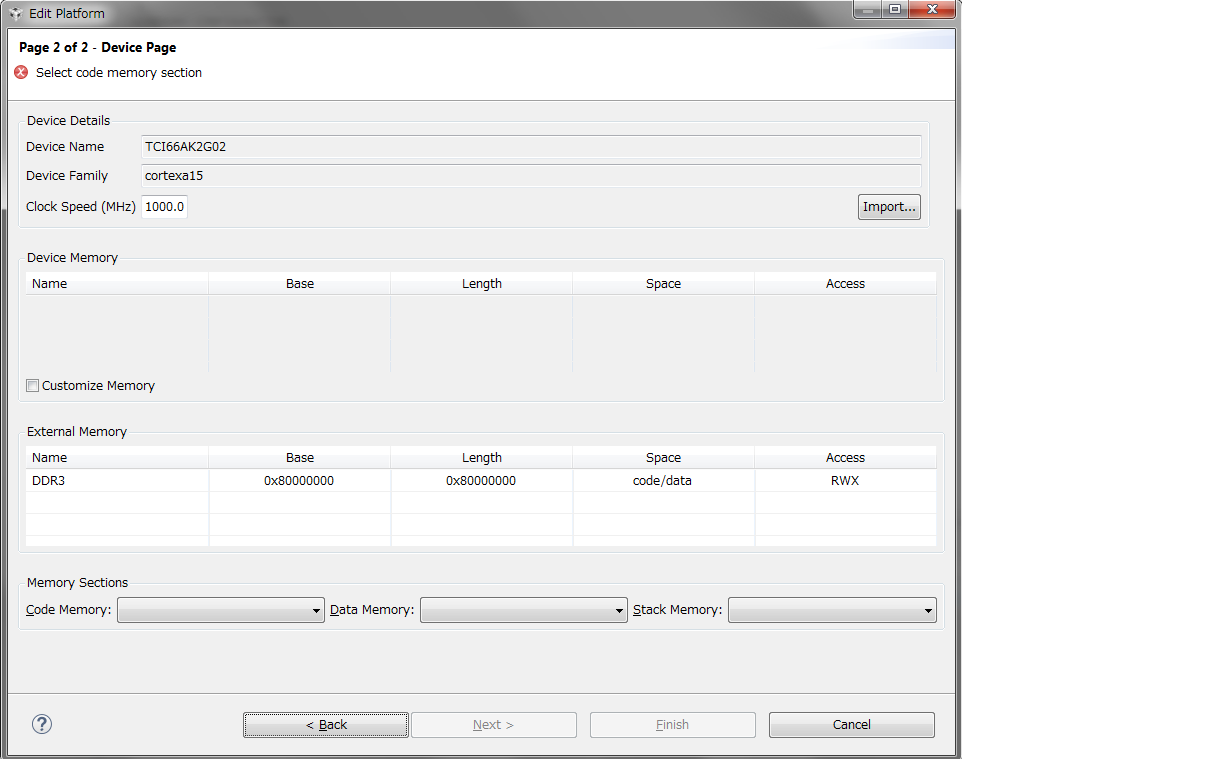

I noticed your PDK example code (for example, GPIO_LedBlink_evmK2G_armExampleProject) for ARM side (CortexA15) did not define 512KB of L2 Memory in RTSC platform (ti.platforms.evmTCI66AK2G02). Please note I'm using pdk_k2g_1_0_2 with bios_6_45_01_29 package. Actually, the platform comes from bios package (C:\ti\bios_6_45_01_29\packages\ti\platforms\evmTCI66AK2G02\Platform.xdc) and that looks below:

metaonly module Platform inherits xdc.platform.IPlatform

{

readonly config xdc.platform.IPlatform.Board BOARD = {

id: "0",

boardName: "evmTCI66AK2G02",

boardFamily: "evmTCI66AK2G02",

boardRevision: null,

};

/* DSP */

readonly config xdc.platform.IExeContext.Cpu DSP = {

id: "0",

clockRate: 1220,

catalogName: "ti.catalog.c6000",

deviceName: "TCI66AK2G02",

revision: "1.0",

};

/* GPP */

readonly config xdc.platform.IExeContext.Cpu GPP = {

id: "1",

clockRate: 1000.0, /* Typically set by the HLOS */

catalogName: "ti.catalog.arm.cortexa15",

deviceName: "TCI66AK2G02",

revision: "1.0"

};

instance:

override readonly config xdc.platform.IPlatform.Memory

externalMemoryMap[string] = [

["DDR3", {name: "DDR3", base: 0x80000000, len: 0x80000000}],

];

/*

* ======== l1PMode ========

* Define the amount of L1P RAM used for L1 Program Cache.

*

* Check the device documentation for valid values.

*/

config String l1PMode = "32k";

/*

* ======== l1DMode ========

* Define the amount of L1D RAM used for L1 Data Cache.

*

* Check the device documentation for valid values.

*/

config String l1DMode = "32k";

/*

* ======== l2Mode ========

* Define the amount of L2 RAM used for L2 Cache.

*

* Check the device documentation for valid values.

*/

config String l2Mode = "0k";

};

This defines DDR3 only and other internal memory definitions are coming from ti/catalog/arm/cortexa15/TCI66AK2G02.xdc, but that defines NOTHING. I also could not find memory map for 512KB of L2 Memory for CortexA15 in the datasheet / TRM. I'm wondering if 512KB of L2 memory is really present on K2G platform....

Best Regards,

Naoki