Hi!

My customers to use the C5505, is under development.

When they have confirmed Idle, problems occurred.

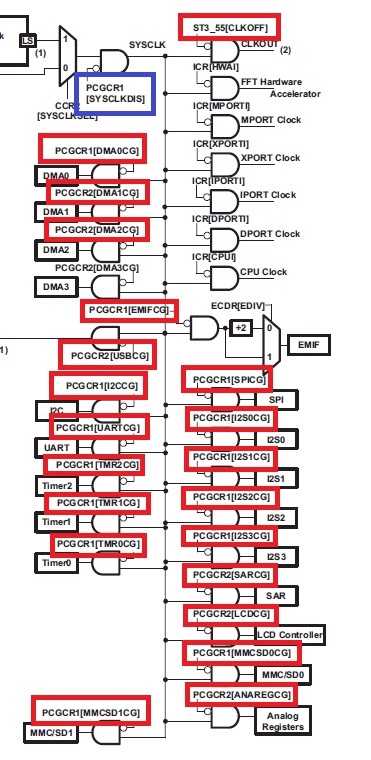

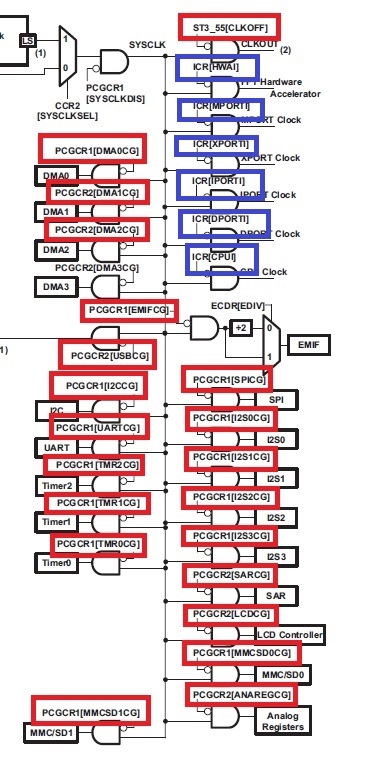

C5505 will enter the power down in PCGCRx or PCGCRn and ICR + idle instruction.

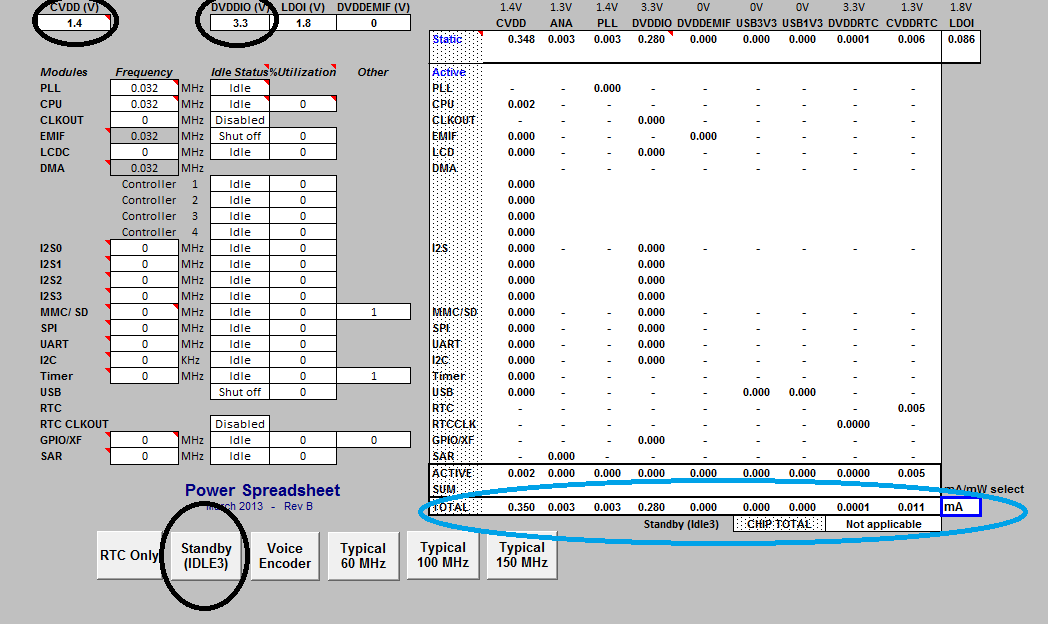

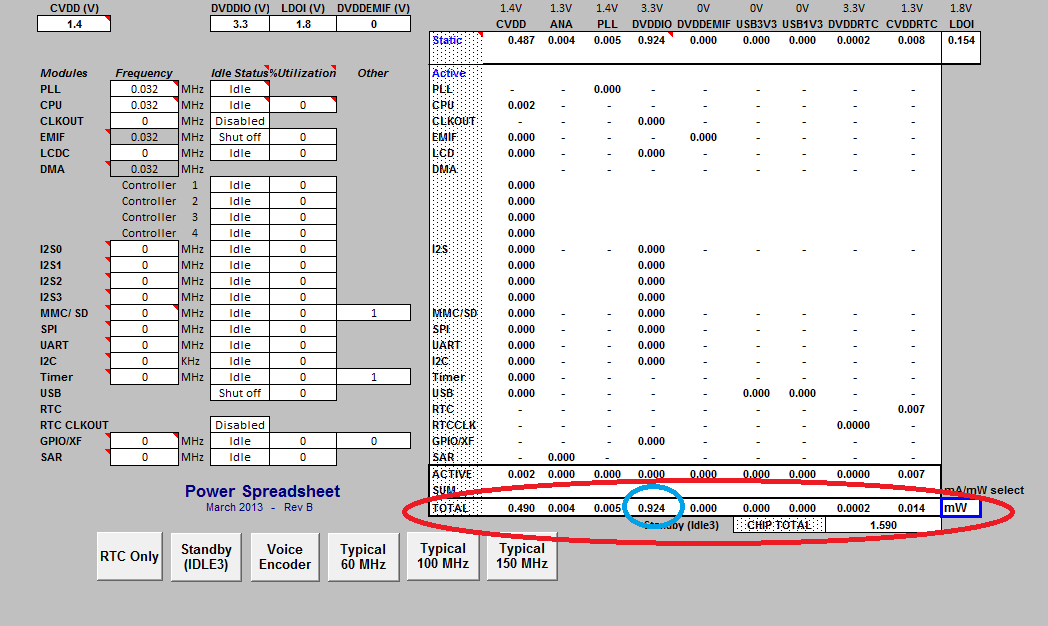

In two cases, the difference of about 1.3mA when measured current has occurred. The reason for this difference?

Case 1. After setting the PCGCRn, it was stopped the set to clock the SYSCLKDIS.

Case 2. After setting the PCGCRn, without setting a SYSCLKDIS, stopped the clock in the ICR + Idle instruction.

*The difference forms in the case when the next order is executed and the case which isn't done. /* System clock disabled */

CSL_FINST(CSL_SYSCTRL_REGS->PCGCR1, SYS_PCGCR1_SYSCLKDIS, DISABLED);

<Source code>

void xxx_Sleep(void)

{

Uint16 reg;

/* Stop UART clock */

reg = CSL_SYSCTRL_REGS->CLKSTOP;

reg |= CSL_SYS_CLKSTOP_URTCLKSTPREQ_MASK;

CSL_SYSCTRL_REGS->CLKSTOP = reg;

while (CSL_FEXT(CSL_SYSCTRL_REGS->CLKSTOP, SYS_CLKSTOP_URTCLKSTPACK)==0);

/* Disable the UART clock */

CSL_FINST(CSL_SYSCTRL_REGS->PCGCR1, SYS_PCGCR1_UARTCG, DISABLED);

/* Disable the I2C clock */

CSL_FINST(CSL_SYSCTRL_REGS->PCGCR1, SYS_PCGCR1_I2CCG, DISABLED);

/* Disable the SPI clock */

CSL_FINST(CSL_SYSCTRL_REGS->PCGCR1, SYS_PCGCR1_SPICG, DISABLED);

/* Disable the I2S clock */

CSL_FINST(CSL_SYSCTRL_REGS->PCGCR1, SYS_PCGCR1_I2S0CG, DISABLED);

CSL_FINST(CSL_SYSCTRL_REGS->PCGCR1, SYS_PCGCR1_I2S1CG, DISABLED);

CSL_FINST(CSL_SYSCTRL_REGS->PCGCR1, SYS_PCGCR1_I2S2CG, DISABLED);

/* Disable the Timer clock */

CSL_FINST(CSL_SYSCTRL_REGS->PCGCR1, SYS_PCGCR1_TMR0CG, DISABLED);

CSL_FINST(CSL_SYSCTRL_REGS->PCGCR1, SYS_PCGCR1_TMR1CG, DISABLED);

CSL_FINST(CSL_SYSCTRL_REGS->PCGCR1, SYS_PCGCR1_TMR2CG, DISABLED);

/* Disable the DMA0, DMA1, DMA2, DMA3 clock */

CSL_FINST(CSL_SYSCTRL_REGS->PCGCR1, SYS_PCGCR1_DMA0CG, DISABLED);

CSL_FINST(CSL_SYSCTRL_REGS->PCGCR2, SYS_PCGCR2_DMA1CG, DISABLED);

CSL_FINST(CSL_SYSCTRL_REGS->PCGCR2, SYS_PCGCR2_DMA2CG, DISABLED);

CSL_FINST(CSL_SYSCTRL_REGS->PCGCR2, SYS_PCGCR2_DMA3CG, DISABLED);

/* Force to BYPASS mode */

CSL_FINST(CSL_SYSCTRL_REGS->CCR2, SYS_CCR2_SYSCLKSEL, BYPASS);

/* PLL stop*/

CSL_SYSCTRL_REGS->CGCR1 = 0xA27C;

/* System clock disabled */

CSL_FINST(CSL_SYSCTRL_REGS->PCGCR1, SYS_PCGCR1_SYSCLKDIS, DISABLED);

/* set CPUI bit in ICR */

*(ioport volatile unsigned int *)(0x0001) = 0x03EF;

CSL_CPU_REGS->IFR0 = 0xFFFF;

CSL_CPU_REGS->IFR1 = 0xFFFF;

C55_disableIER0( C55_IFG02 ); /* INT0 */

C55_disableIER0( C55_IFG03 ); /* INT1 */

C55_disableIER0( C55_IFG04 ); /* TINT */

C55_disableIER0( C55_IFG08 ); /* DMA */

C55_disableIER1( C55_IFG018 ); /* Wakeup */

/* Go to sleep */

asm(" NOP");

asm(" NOP");

asm(" NOP");

asm(" NOP");

asm(" NOP");

asm(" NOP");

asm(" NOP");

asm(" idle");

asm(" NOP");

asm(" NOP");

asm(" NOP");

asm(" NOP");

asm(" NOP");

asm(" NOP");

asm(" NOP");

}

In the figure below, to set the SYSCLKDIS, not difference of 1.3mA has occurred.

* CLKOUT was turned off, but an electric current didn't fall so much.

Regards,