Hello Team,

My customer is using TDA2Eco in Surround View System, and is asking how to modify data (DQ) setup/hold time to DQS/DQS#.

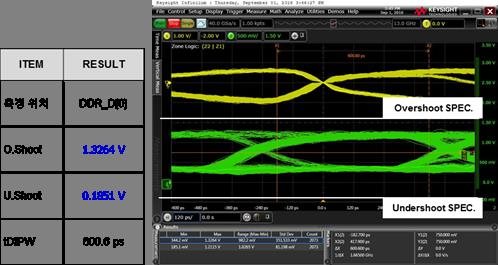

The screen shot of DQ (green) and DQS/DQS# (yellow) is captured as following, and it shows DQS leans to one side of DQ.

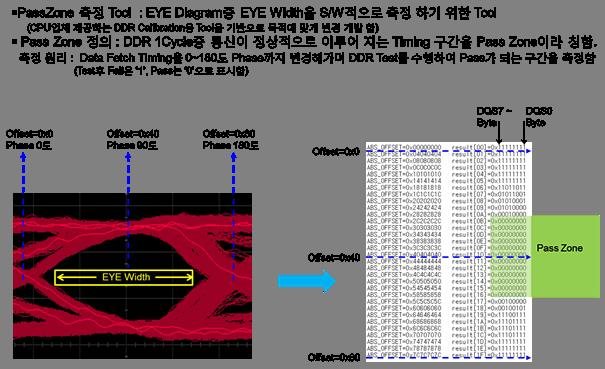

Customer would like to tune the position of DQS to the center of DQ for the stable ddr3 write operation.

They tried below test, but there is no improvement.

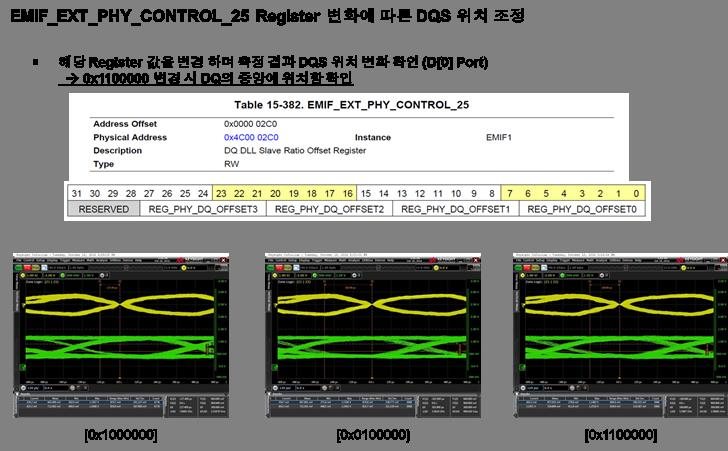

- When customer tried to change the value of "EMIF_EXT_PHY_CONTROL_17~20", waveform is not changed.

- When customer tried to change the value of PHY_REG_WR_DQS_SLAVE_D in "EMIF_EXT_PHY_CONTROL_23", waveform is not changed.

- When customer tried to change the value of PHY_REG_WR_DQS_SLAVE_D in "EMIF_EXT_PHY_CONTROL_23" and DLL_OVERRIDE=1, system becomes lock up.

Could you guide which register can be configured to modify data (DQ) setup/hold time to DQS/DQS#?

If there is any procedure to configure, please let me know as well.

Thank you.

[Waveform - DQS/DQS# and DQ]

[Register - EMIF_EXT_PHY_CONTROL_23]

regards,

Lloyd Hwang