On the Jacinto6 (DRA75x/74x), the MMC1 supports Default speed (DS) and High speed (HS) for 3.3V operation.

However, I could not find any register which is controlled to switch MMC1 host controller to these two modes.

Only we can change MMC Clock Frequency.

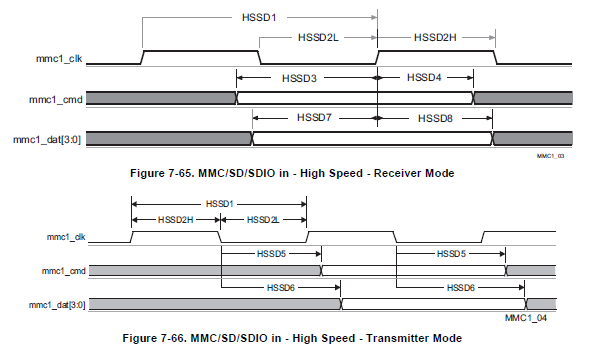

From Data Manual, AC timing of these two modes are different. Not only Maximum Clock Frequency, but also Delay Time of Switching Characteristics and Setup/Hold Time of Timing Requirements.

How MMC host controller determine these two modes ? and change Switching Characteristics/Timing Requirements ?

Best Regards,

Yasuhiro Mitsui