We are using cs0 to link with fpga memory mapped registers using ti 5728 eval board. Able to write fine but unable to read. read data is 0. I follwed the GPMC_AD signals on scope up to the pin and it is correct but the read is always 0.

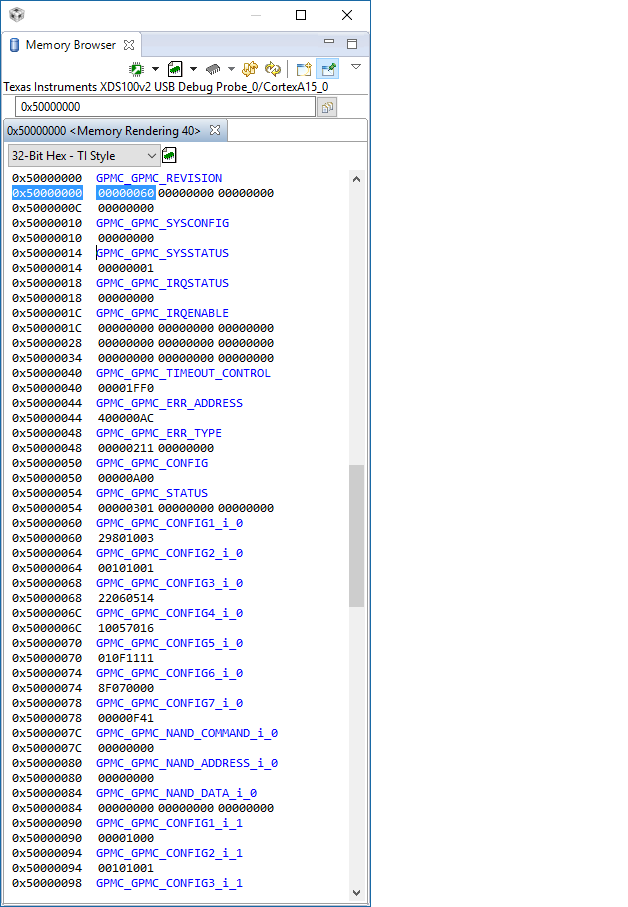

gpmc read non multiplexed gpmc_config.dat

gpmc_config.dat