Part Number: AM3352

Other Parts Discussed in Thread: TPS65910, TPS65217

Hi,

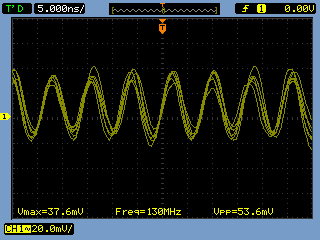

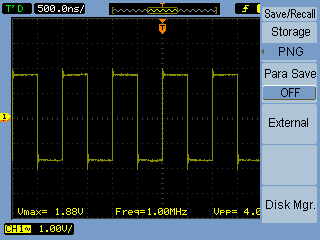

We are using AM3352 ZCZ Package with Marvell 88E1512 PHY device in our customised board.We have made RGMII configuration as in AM335x starter kit.While testing Link is UP.Ping is not happening.No activity on the wireshark.While debugging found that RGMII TX_ClK is not coming but RX_Clk from PHY is coming.The console log is shown below.

Starting kernel ...

Uncompressing Linux... done, booting the kernel.

[ 0.000000] Linux version 3.2.0 (root@rrtestpc-ThinkCentre-A58) (gcc version 4.7.3 20130226 (prerelease) (crosstool-NG linaro-1.13.1-4.7-2013.

03-20130313 - Linaro GCC 2013.03) ) #17 Wed Dec 14 15:21:23 IST 2016

[ 0.000000] CPU: ARMv7 Processor [413fc082] revision 2 (ARMv7), cr=10c53c7d

[ 0.000000] CPU: PIPT / VIPT nonaliasing data cache, VIPT aliasing instruction cache

[ 0.000000] Machine: am335xevm

[ 0.000000] Memory policy: ECC disabled, Data cache writeback

[ 0.000000] AM335X ES2.1 (neon )

[ 0.000000] Built 1 zonelists in Zone order, mobility grouping on. Total pages: 130048

[ 0.000000] Kernel command line: console=ttyO0,115200n8 root=/dev/mmcblk0p2 ro rootfstype=ext3 rootwait ip=none

[ 0.000000] PID hash table entries: 2048 (order: 1, 8192 bytes)

[ 0.000000] Dentry cache hash table entries: 65536 (order: 6, 262144 bytes)

[ 0.000000] Inode-cache hash table entries: 32768 (order: 5, 131072 bytes)

[ 0.000000] Memory: 512MB = 512MB total

[ 0.000000] Memory: 514012k/514012k available, 10276k reserved, 0K highmem

[ 0.000000] Virtual kernel memory layout:

[ 0.000000] vector : 0xffff0000 - 0xffff1000 ( 4 kB)

[ 0.000000] fixmap : 0xfff00000 - 0xfffe0000 ( 896 kB)

[ 0.000000] vmalloc : 0xe0800000 - 0xff000000 ( 488 MB)

[ 0.000000] lowmem : 0xc0000000 - 0xe0000000 ( 512 MB)

[ 0.000000] modules : 0xbf000000 - 0xc0000000 ( 16 MB)

[ 0.000000] .text : 0xc0008000 - 0xc04df000 (4956 kB)

[ 0.000000] .init : 0xc04df000 - 0xc0515000 ( 216 kB)

[ 0.000000] .data : 0xc0516000 - 0xc056e128 ( 353 kB)

[ 0.000000] .bss : 0xc056e14c - 0xc059a044 ( 176 kB)

[ 0.000000] NR_IRQS:396

[ 0.000000] IRQ: Found an INTC at 0xfa200000 (revision 5.0) with 128 interrupts

[ 0.000000] Total of 128 interrupts on 1 active controller

[ 0.000000] OMAP clockevent source: GPTIMER2 at 25000000 Hz

[ 0.000000] OMAP clocksource: GPTIMER1 at 32768 Hz

[ 0.000000] sched_clock: 32 bits at 32kHz, resolution 30517ns, wraps every 131071999ms

[ 0.000000] Console: colour dummy device 80x30

[ 0.000061] Calibrating delay loop... 996.14 BogoMIPS (lpj=4980736)

[ 0.089263] pid_max: default: 32768 minimum: 301

[ 0.089355] Security Framework initialized

[ 0.089416] Mount-cache hash table entries: 512

[ 0.089721] CPU: Testing write buffer coherency: ok

[ 0.090301] devtmpfs: initialized

[ 0.109039] omap_hwmod: gfx: failed to hardreset

[ 0.124694] omap_hwmod: pruss: failed to hardreset

[ 0.125579] print_constraints: dummy:

[ 0.125854] NET: Registered protocol family 16

[ 0.127441] OMAP GPIO hardware version 0.1

[ 0.129272] omap_mux_init: Add partition: #1: core, flags: 0

[ 0.130767] omap_i2c.1: alias fck already exists

[ 0.131439] omap2_mcspi.1: alias fck already exists

[ 0.131622] omap2_mcspi.2: alias fck already exists

[ 0.132293] edma.0: alias fck already exists

[ 0.132324] edma.0: alias fck already exists

[ 0.132324] edma.0: alias fck already exists

[ 0.145599] bio: create slab <bio-0> at 0

[ 0.147186] SCSI subsystem initialized

[ 0.148529] omap_i2c omap_i2c.1: bus 1 rev2.4.0 at 100 kHz

[ 0.149658] tps65910 1-002d: could not be detected

[ 0.151428] Switching to clocksource gp timer

[ 0.164794] NET: Registered protocol family 2

[ 0.164947] IP route cache hash table entries: 4096 (order: 2, 16384 bytes)

[ 0.165191] TCP established hash table entries: 16384 (order: 5, 131072 bytes)

[ 0.165405] TCP bind hash table entries: 16384 (order: 4, 65536 bytes)

[ 0.165527] TCP: Hash tables configured (established 16384 bind 16384)

[ 0.165557] TCP reno registered

[ 0.165557] UDP hash table entries: 256 (order: 0, 4096 bytes)

[ 0.165557] UDP-Lite hash table entries: 256 (order: 0, 4096 bytes)

[ 0.165710] NET: Registered protocol family 1

[ 0.165924] RPC: Registered named UNIX socket transport module.

[ 0.165954] RPC: Registered udp transport module.

[ 0.165954] RPC: Registered tcp transport module.

[ 0.165954] RPC: Registered tcp NFSv4.1 backchannel transport module.

[ 0.166137] NetWinder Floating Point Emulator V0.97 (double precision)

[ 0.182952] VFS: Disk quotas dquot_6.5.2

[ 0.183013] Dquot-cache hash table entries: 1024 (order 0, 4096 bytes)

[ 0.183654] msgmni has been set to 1003

[ 0.186035] alg: No test for stdrng (krng)

[ 0.186645] io scheduler noop registered

[ 0.186645] io scheduler deadline registered

[ 0.186706] io scheduler cfq registered (default)

[ 0.187652] omap_uart.0: ttyO0 at MMIO 0x44e09000 (irq = 72) is a OMAP UART0

[ 0.616210] console [ttyO0] enabled

[ 0.620361] omap_uart.1: ttyO1 at MMIO 0x48022000 (irq = 73) is a OMAP UART1

[ 0.628112] omap_uart.2: ttyO2 at MMIO 0x48024000 (irq = 74) is a OMAP UART2

[ 0.635833] omap_uart.3: ttyO3 at MMIO 0x481a6000 (irq = 44) is a OMAP UART3

[ 0.643585] omap_uart.4: ttyO4 at MMIO 0x481a8000 (irq = 45) is a OMAP UART4

[ 0.651275] omap_uart.5: ttyO5 at MMIO 0x481aa000 (irq = 46) is a OMAP UART5

[ 0.659393] omap4_rng omap4_rng: OMAP4 Random Number Generator ver. 2.00

[ 0.673736] brd: module loaded

[ 0.680694] loop: module loaded

[ 0.684173] i2c-core: driver [tsl2550] using legacy suspend method

[ 0.690612] i2c-core: driver [tsl2550] using legacy resume method

[ 0.697052] at24 1-0051: 32768 byte 24c256 EEPROM, writable, 64 bytes/write

[ 0.801666] No daughter card found

[ 0.805236] at24 1-0050: 32768 byte 24c256 EEPROM, writable, 64 bytes/write

[ 0.820404] Board name: A335BNLT

[ 0.823791] Board version: 000C

[ 0.827056] The board is a AM335x Beaglebone Black.

[ 0.834167] tps65217 1-0024: TPS65217 ID 0xe version 1.2

[ 0.841674] print_constraints: DCDC1: 900 <--> 1800 mV at 1500 mV

[ 0.850067] print_constraints: DCDC2: 900 <--> 3300 mV at 1325 mV

[ 0.858459] print_constraints: DCDC3: 900 <--> 1500 mV at 1125 mV

[ 0.866851] print_constraints: LDO1: 1000 <--> 3300 mV at 1800 mV

[ 0.875213] print_constraints: LDO2: 900 <--> 3300 mV at 3300 mV

[ 0.883514] print_constraints: LDO3: 1800 <--> 3300 mV at 1800 mV

[ 0.891876] print_constraints: LDO4: 1800 <--> 3300 mV at 3300 mV

[ 0.899139] omap_hsmmc.0: alias fck already exists

[ 0.904571] omap_hsmmc.1: alias fck already exists

[ 0.909942] omap_i2c.3: alias fck already exists

[ 0.915161] omap_i2c omap_i2c.3: bus 3 rev2.4.0 at 100 kHz

[ 0.922454] registered am33xx_sr device

[ 0.927917] mtdoops: mtd device (mtddev=name/number) must be supplied

[ 0.934967] omap2-nand driver initializing

[ 0.939392] OneNAND driver initializing

[ 0.950103] CAN device driver interface

[ 0.954162] CAN bus driver for Bosch D_CAN controller 1.0

[ 1.001708] davinci_mdio davinci_mdio.0: davinci mdio revision 1.6

[ 1.008178] davinci_mdio davinci_mdio.0: detected phy mask fffffffc

[ 1.015838] davinci_mdio.0: probed

[ 1.019378] davinci_mdio davinci_mdio.0: phy[0]: device 0:00, driver Marvell 88E1512

[ 1.027496] davinci_mdio davinci_mdio.0: phy[1]: device 0:01, driver Marvell 88E1512

[ 1.036132] mousedev: PS/2 mouse device common for all mice

[ 1.042968] omap_rtc am33xx-rtc: rtc core: registered am33xx-rtc as rtc0

[ 1.050170] i2c /dev entries driver

[ 1.332641] OMAP Watchdog Timer Rev 0x01: initial timeout 60 sec

[ 1.340087] cpuidle: using governor ladder

[ 1.344757] cpuidle: using governor menu

[ 1.352081] omap4_aes_mod_init: loading AM33X AES driver

[ 1.357727] omap4-aes omap4-aes: AM33X AES hw accel rev: 3.02

[ 1.364379] omap4_aes_probe: probe() done

[ 1.368774] omap4_sham_mod_init: loading AM33X SHA/MD5 driver

[ 1.374877] omap4-sham omap4-sham: AM33X SHA/MD5 hw accel rev: 4.03

[ 1.388458] omap4_sham_probe: probe() done

[ 1.396179] oprofile: hardware counters not available

[ 1.401489] oprofile: using timer interrupt.

[ 1.405975] nf_conntrack version 0.5.0 (8031 buckets, 32124 max)

[ 1.412689] ip_tables: (C) 2000-2006 Netfilter Core Team

[ 1.418334] TCP cubic registered

[ 1.421722] NET: Registered protocol family 17

[ 1.426391] can: controller area network core (rev 20090105 abi 8)

[ 1.432922] NET: Registered protocol family 29

[ 1.437561] can: raw protocol (rev 20090105)

[ 1.442047] can: broadcast manager protocol (rev 20090105 t)

[ 1.447998] Registering the dns_resolver key type

[ 1.452972] VFP support v0.3: implementor 41 architecture 3 part 30 variant c rev 3

[ 1.460968] ThumbEE CPU extension supported.

[ 1.465515] mux: Failed to setup hwmod io irq -22

[ 1.470947] Power Management for AM33XX family

[ 1.475799] Trying to load am335x-pm-firmware.bin (60 secs timeout)

[ 1.482513] Copied the M3 firmware to UMEM

[ 1.486846] Cortex M3 Firmware Version = 0x181

[ 1.492279] create_regulator: DCDC2: Failed to create debugfs directory

[ 1.499847] smartreflex smartreflex: am33xx_sr_probe: Driver initialized

[ 1.510772] clock: disabling unused clocks to save power

[ 1.525878] Detected MACID=84:eb:18:b2:55:d0

[ 1.531250] cpsw: Detected MACID = 84:eb:18:b2:55:d2

[ 1.537353] omap_rtc am33xx-rtc: setting system clock to 2000-01-01 00:00:01 UTC (946684801)

[ 1.546661] Waiting for root device /dev/mmcblk0p2...

[ 1.584320] mmc0: host does not support reading read-only switch. assuming write-enable.

[ 1.595886] mmc0: new high speed SDHC card at address aaaa

[ 1.602111] mmcblk0: mmc0:aaaa SU04G 3.69 GiB

[ 1.608306] mmcblk0: p1 p2

[ 1.667602] kjournald starting. Commit interval 5 seconds

[ 1.673400] EXT3-fs (mmcblk0p2): mounted filesystem with ordered data mode

[ 1.680633] VFS: Mounted root (ext3 filesystem) readonly on device 179:2.

[ 1.689178] devtmpfs: mounted

[ 1.692565] Freeing init memory: 216K

[ 1.853240] EXT3-fs (mmcblk0p2): using internal journal

Starting logging: OK

Initializing random number generator... done.

Starting network: OK

Starting DHCP server: FAIL

Welcome to Buildroot

buildroot login: root

# ifconfig eth0 10.3.3.15 up

[ 22.280578] net eth0: CPSW phy found : id is : 0x1410dd1

# [ 34.273376] Trying 1000/FULL

[ 35.272796] PHY: 0:00 - Link is Up - 1000/Full

# ping 10.3.3.17

PING 10.3.3.17 (10.3.3.17): 56 data bytes

^C

--- 10.3.3.17 ping statistics ---

5 packets transmitted, 0 packets received, 100% packet loss

# ethtool -s eth0 speed 100 duplex full autoneg 0ff

ethtool: bad command line argument(s)

For more information run ethtool -h

# ethtool -s eth0 speed 100 duplex full autoneg off

# [ 140.272827] PHY: 0:00 - Link is Up - 100/Full

#

#

# ping 10.3.3.17

PING 10.3.3.17 (10.3.3.17): 56 data bytes

^C

--- 10.3.3.17 ping statistics ---

9 packets transmitted, 0 packets received, 100% packet loss

# ethtool eth0

Settings for eth0:

Supported ports: [ TP MII ]

Supported link modes: 10baseT/Half 10baseT/Full

100baseT/Half 100baseT/Full

1000baseT/Half 1000baseT/Full

Supported pause frame use: No

Supports auto-negotiation: Yes

Advertised link modes: 100baseT/Full

Advertised pause frame use: No

Advertised auto-negotiation: No

Speed: 100Mb/s

Duplex: Full

Port: MII

PHYAD: 0

Transceiver: external

Auto-negotiation: off

Current message level: 0x00000000 (0)

Link detected: yes

#

I found that we should provide TX_clk delay from PHY device.Is this issue causing problem ? or Processor is unable to generate TX_clk ?

Please suggest any driver configurations to be changed or any processor registers to be configured along with files path.

Thanks in advance.