Good morning.

We are currently evaluating the Sitara processor for one of our projects. We need to interface with an FPGA through PCIe. Ideally, we would want to run the PCIe software in the M4 so that we can use the available MIPS on the A15 and the C66 to perform other activities.

From the looks of it, PCIe is indeed supported in the M4 core using Sys/Bios. I was able to generate the example project and compile it through with Code Composer today. However, when I run the code, I get a crash when enabling the PCIe clocks in the PlatformPCIESS1ClockEnable function:

void PlatformPCIESS1ClockEnable(void)

{

uint32_t regVal;

/*OCP2SCP1 enables accessing the PCIe PHY serial configuration*/

HW_WR_FIELD32(SOC_L3INIT_CM_CORE_BASE + CM_L3INIT_OCP2SCP1_CLKCTRL,

CM_L3INIT_OCP2SCP1_CLKCTRL_MODULEMODE,

CM_L3INIT_OCP2SCP1_CLKCTRL_MODULEMODE_AUTO);

/*OCP2SCP3 enables accessing the PCIe PHY serial configuration*/

HW_WR_FIELD32(SOC_L3INIT_CM_CORE_BASE + CM_L3INIT_OCP2SCP3_CLKCTRL,

CM_L3INIT_OCP2SCP3_CLKCTRL_MODULEMODE,

CM_L3INIT_OCP2SCP3_CLKCTRL_MODULEMODE_AUTO);

/*PCIeSS CLKSTCTRL SW WakeUp*/

HW_WR_FIELD32(SOC_L3INIT_CM_CORE_BASE + CM_PCIE_CLKSTCTRL,

CM_PCIE_CLKSTCTRL_CLKTRCTRL,

CM_PCIE_CLKSTCTRL_CLKTRCTRL_SW_WKUP);

/*L3 Init PCIeSS1 CLKCTRL SW Enable*/

HW_WR_FIELD32(SOC_L3INIT_CM_CORE_BASE + CM_PCIE_PCIESS1_CLKCTRL,

CM_PCIE_PCIESS1_CLKCTRL_MODULEMODE,

CM_PCIE_PCIESS1_CLKCTRL_MODULEMODE_ENABLED);

while ((HW_RD_REG32(SOC_L3INIT_CM_CORE_BASE + CM_PCIE_PCIESS1_CLKCTRL) &

CM_PCIE_PCIESS1_CLKCTRL_IDLEST_MASK) !=

CM_PCIE_PCIESS1_CLKCTRL_IDLEST_FUNC)

{

;

}

/*Enable PCIe PHY optional clk*/

regVal = HW_RD_REG32(SOC_L3INIT_CM_CORE_BASE + CM_PCIE_PCIESS1_CLKCTRL);

HW_SET_FIELD(regVal, CM_PCIE_PCIESS1_CLKCTRL_OPTFCLKEN_PCIEPHY_CLK_DIV,

CM_PCIE_PCIESS1_CLKCTRL_OPTFCLKEN_PCIEPHY_CLK_DIV_FCLK_EN);

HW_SET_FIELD(regVal, CM_PCIE_PCIESS1_CLKCTRL_OPTFCLKEN_PCIEPHY_CLK,

CM_PCIE_PCIESS1_CLKCTRL_OPTFCLKEN_PCIEPHY_CLK_FCLK_EN);

HW_SET_FIELD(regVal, CM_PCIE_PCIESS1_CLKCTRL_OPTFCLKEN_32KHZ,

CM_PCIE_PCIESS1_CLKCTRL_OPTFCLKEN_32KHZ_FCLK_EN);

HW_WR_REG32(SOC_L3INIT_CM_CORE_BASE + CM_PCIE_PCIESS1_CLKCTRL, regVal);

}

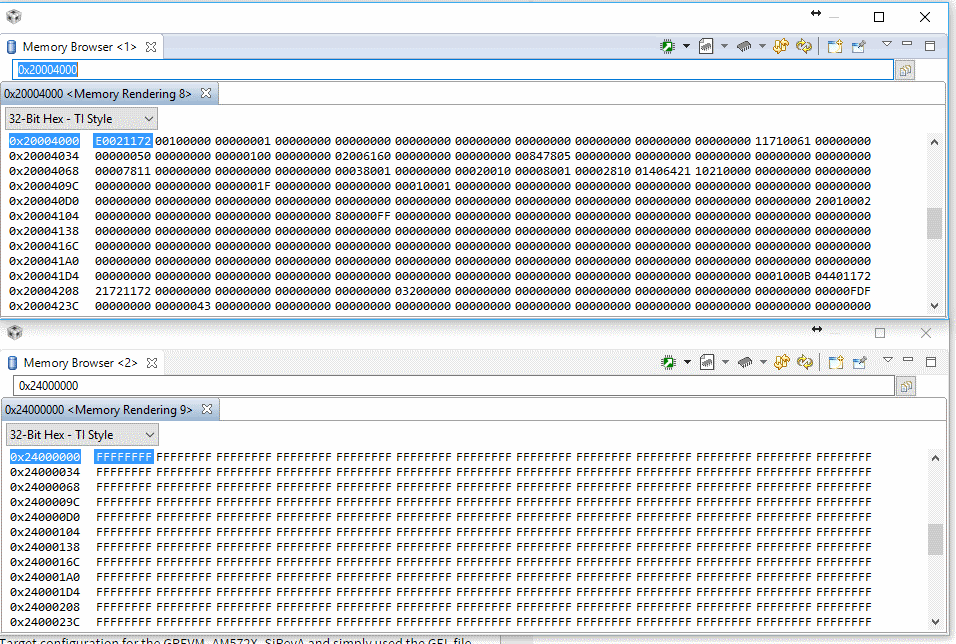

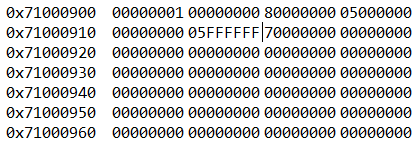

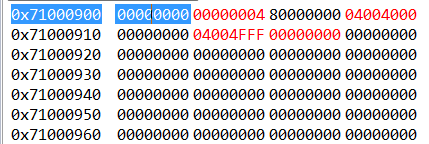

I suspect this is crashing because the M4 doesn't have access to the registers it is trying to write to.

My question is how can I make these registers (and all other required PCIe memory region) available on the M4?

Best Regards,

- David