Hi,

I have a qestion about I2S2 of C5517 device, My customer's board has problems not outputting data from I2S2.

Details are shown below:

C5517 is I2S master, it connects to the slave microcomputer as shown below.

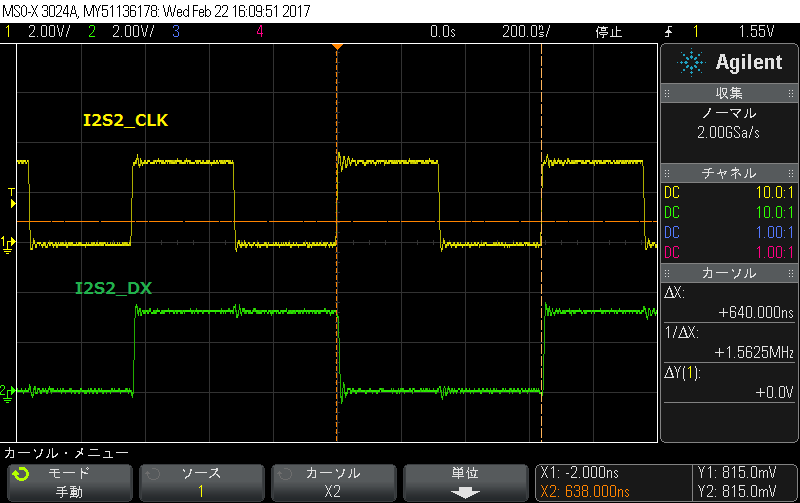

The CLK signal and the frame sync are normally output but every TX data are not output correctly, the same phenomenon occurs even if data is written directly to the TX buffer by CCS.

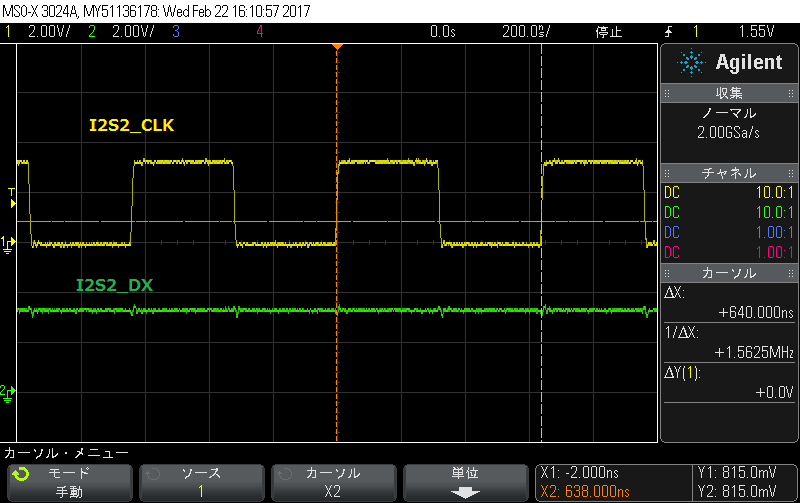

It has been confirmed that the problem is solved by the following method.

Method 1:

Cut the pattern between I2S2_CLK and Test port.

Method 2:

Change the I2S2SCTRL.DATADLY bit setting form 1 bit data delay to 2 bit. or, Use DSP format instead of I2S format.

It seems that there are some restrictions when C5517 is used as an I2S master.

Especially, Does C5517 has restrictions on the pattern length and load capacity of the I2S clock line?

Best regards,

H.U