hi,

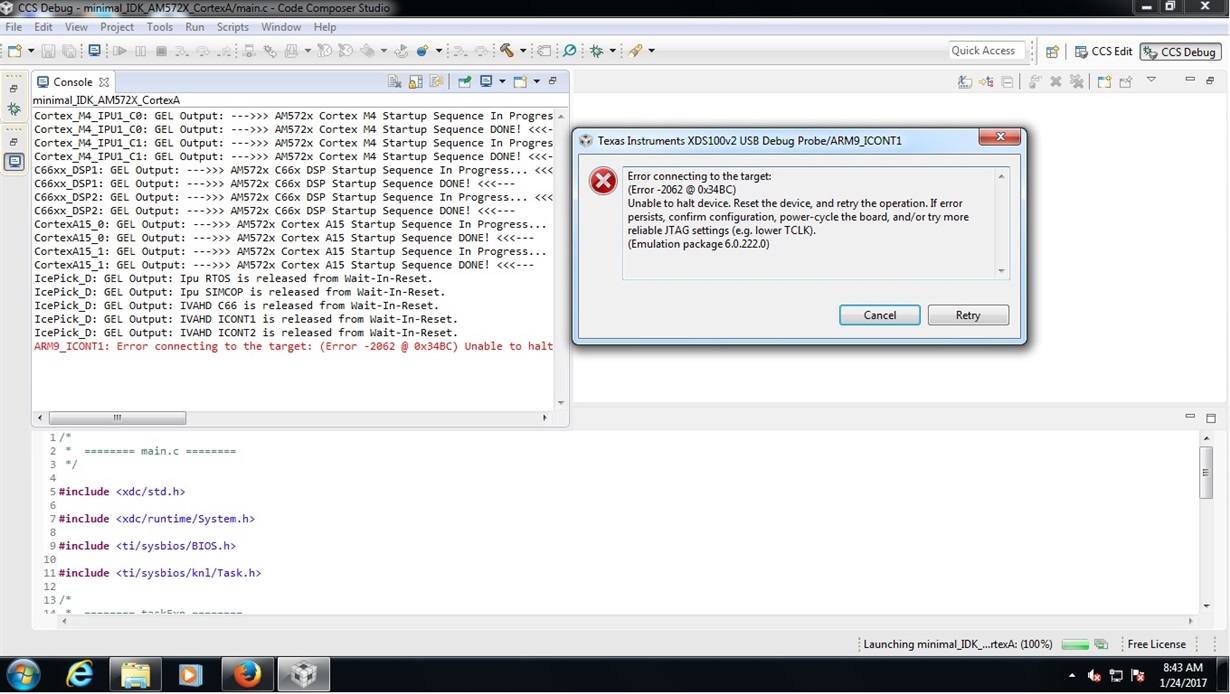

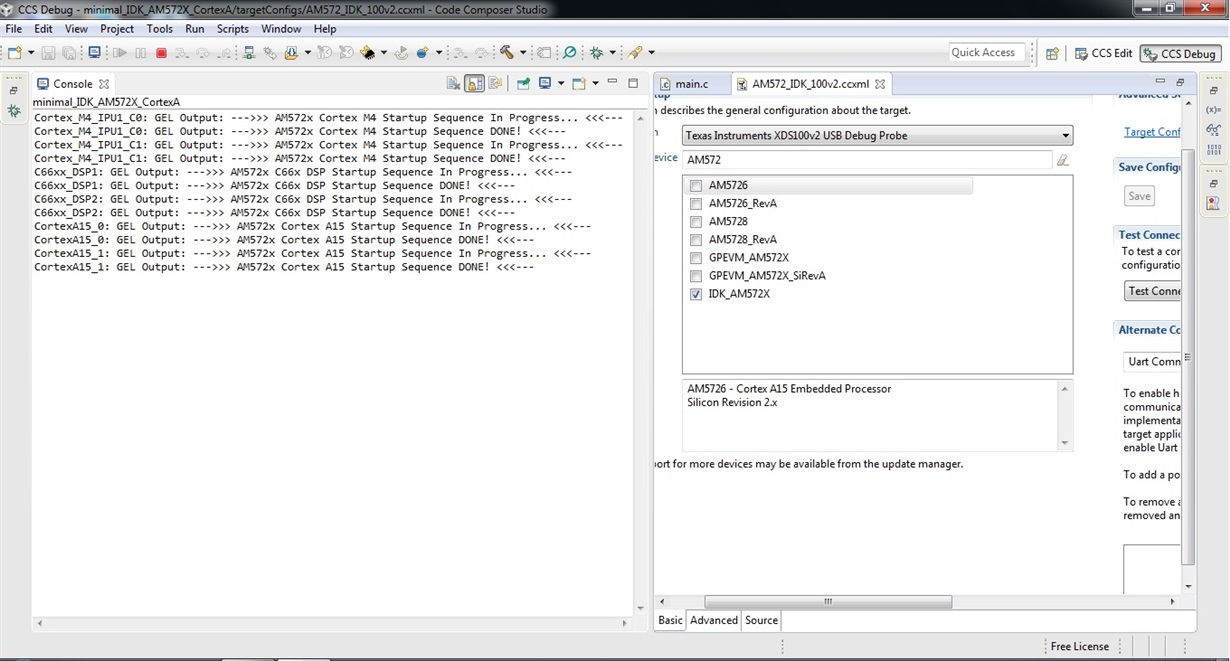

I am new to this TI processor and CCS. I am first time using this setup. i am unable to boot the board with provided SD card. I have gone through the process of creating prebuild image with TI Rtos SDK. on different SD Card but unable to get result on teraterm with baud rate of 115200 terminal dosent show any thing.

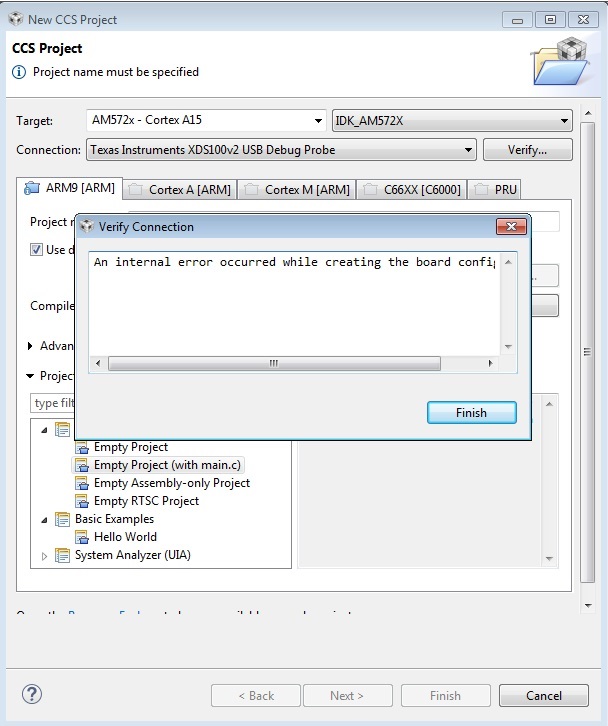

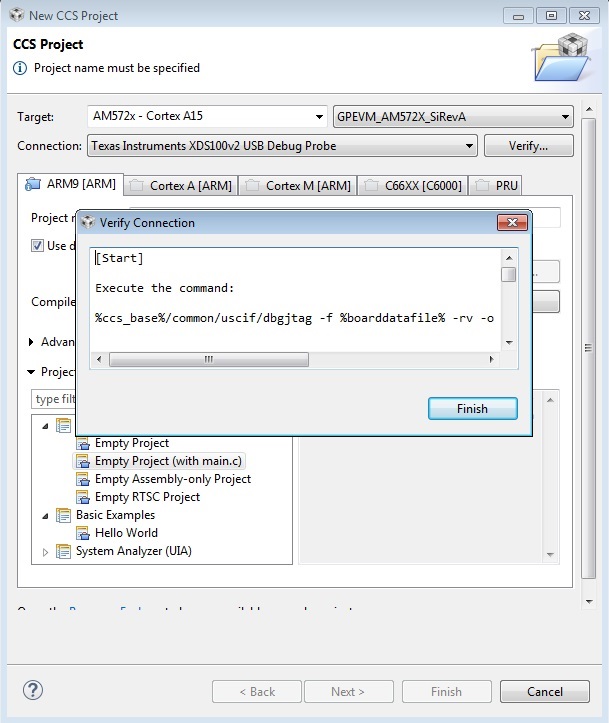

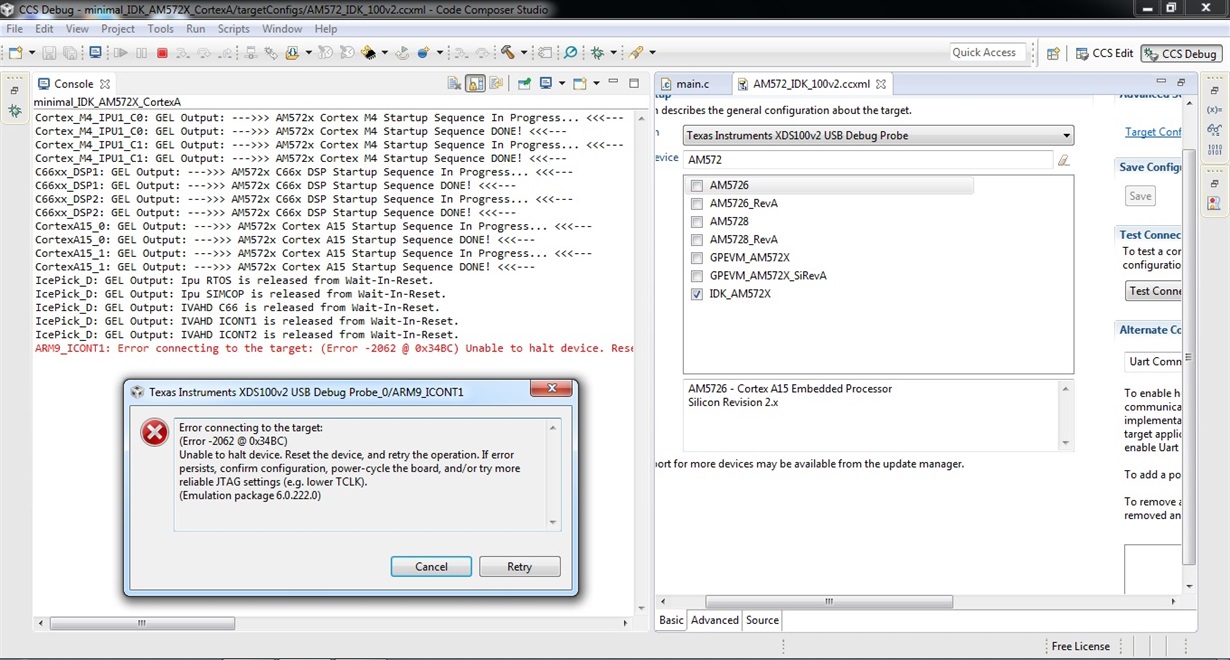

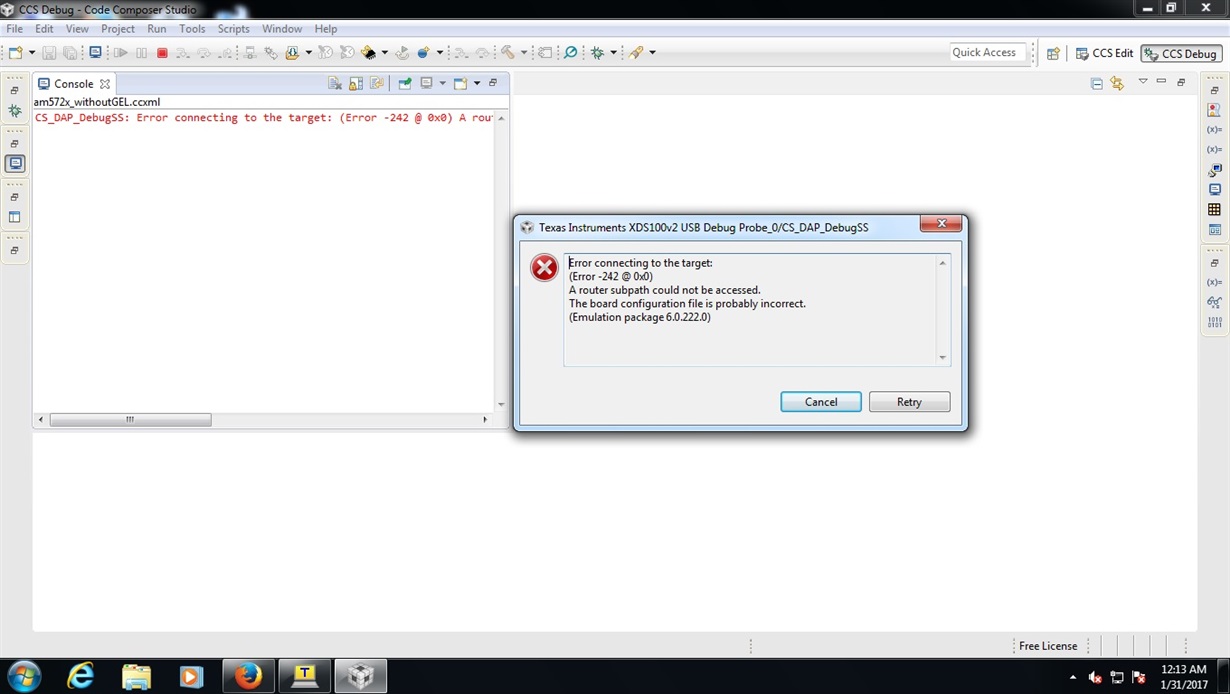

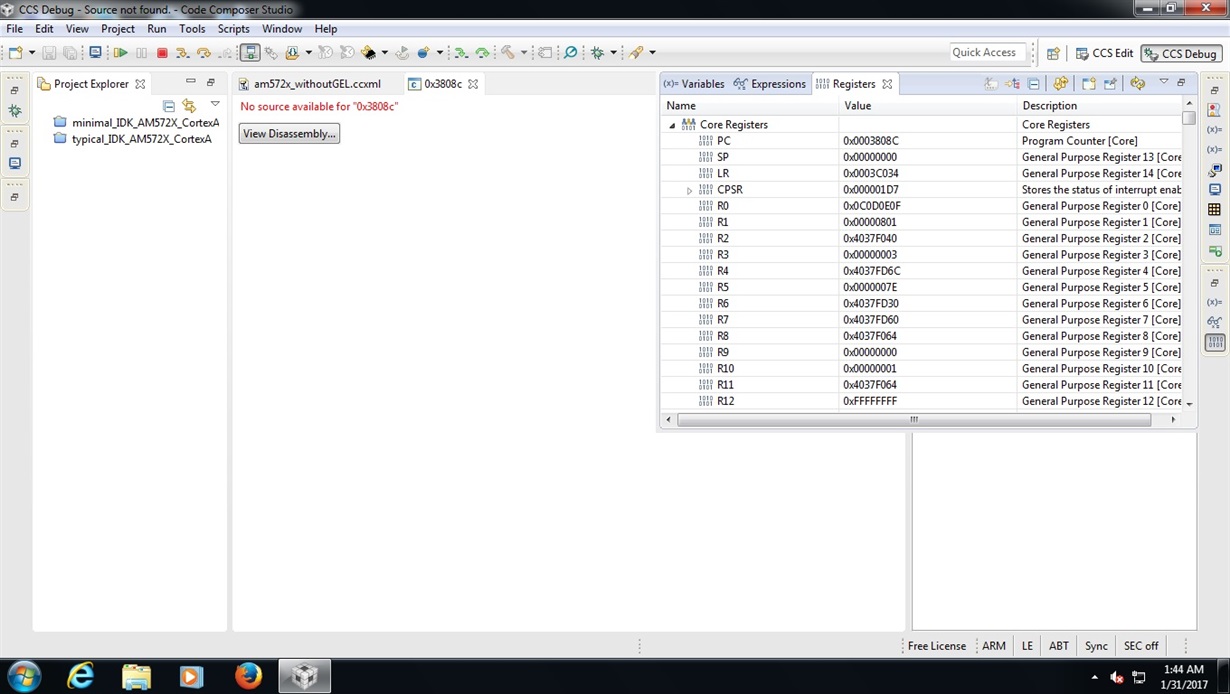

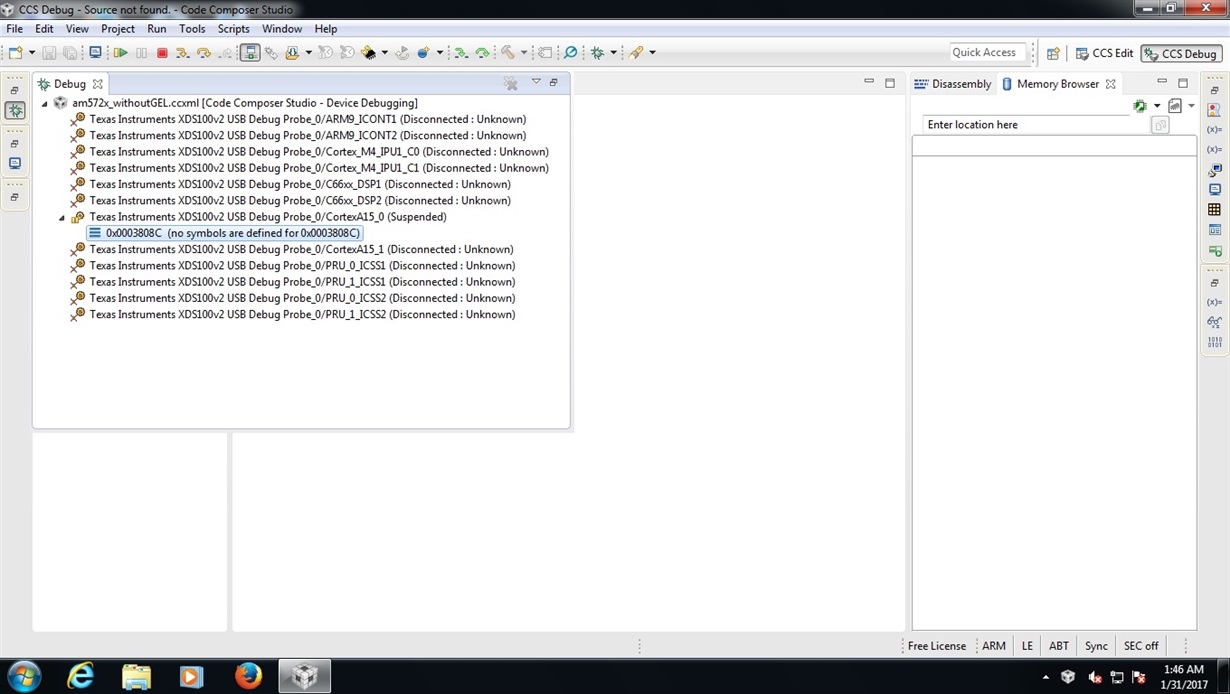

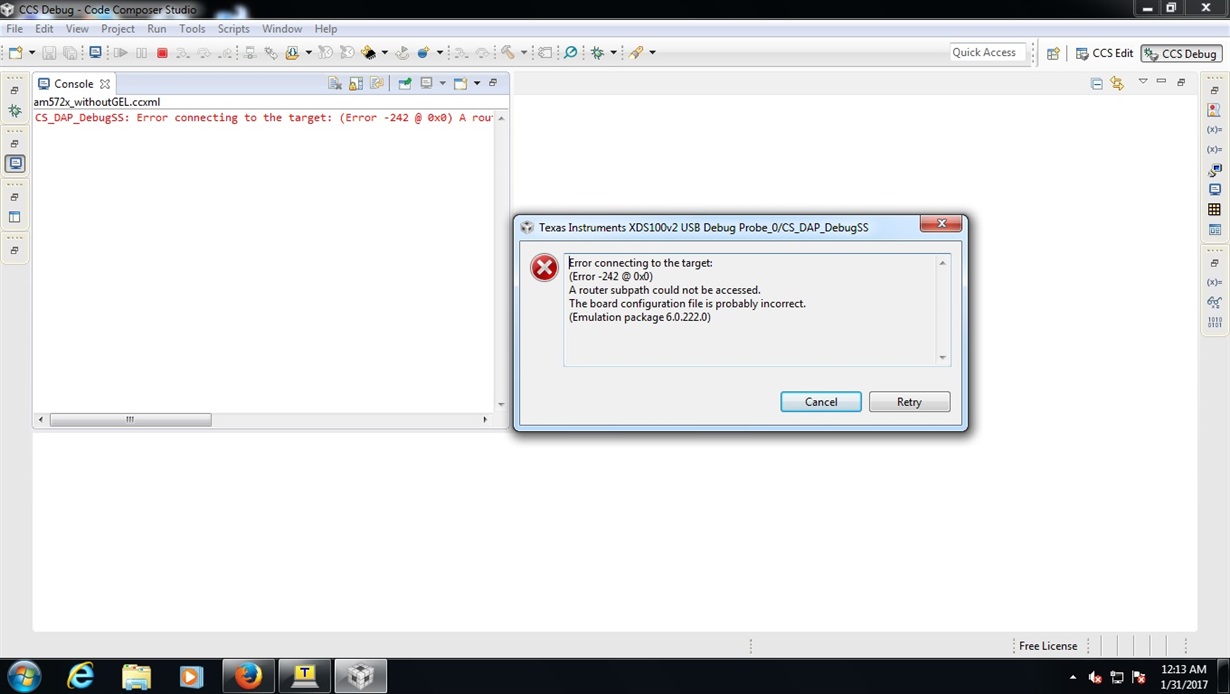

also when i run the ccs 7 and on selecting XDS100V2 USB Emulation and after clicking verify button, it display internal error occured.

I am using 5V 2 amp power supply.

Thanks in advance,

Regards,

Nikhil