Dear,

I am working on AM4378 project and it is based on AM437x-gp-evm. I built sitara linux and boot from SD card now. It is working fine.

Now I wanted to transfer all linux files(MLO, uboot.img, kernel, file system, etc) to eMMC and boot it from eMMC. How do i achieve this?

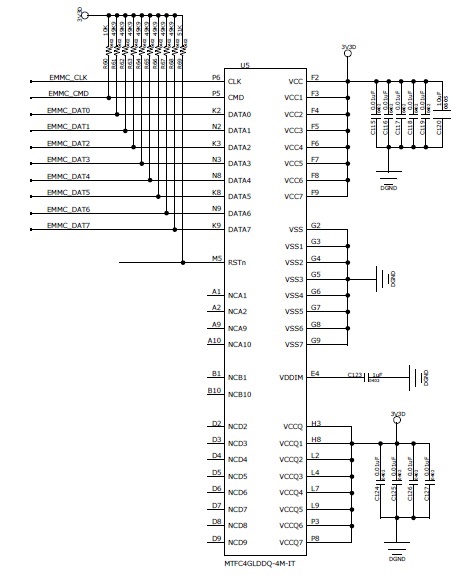

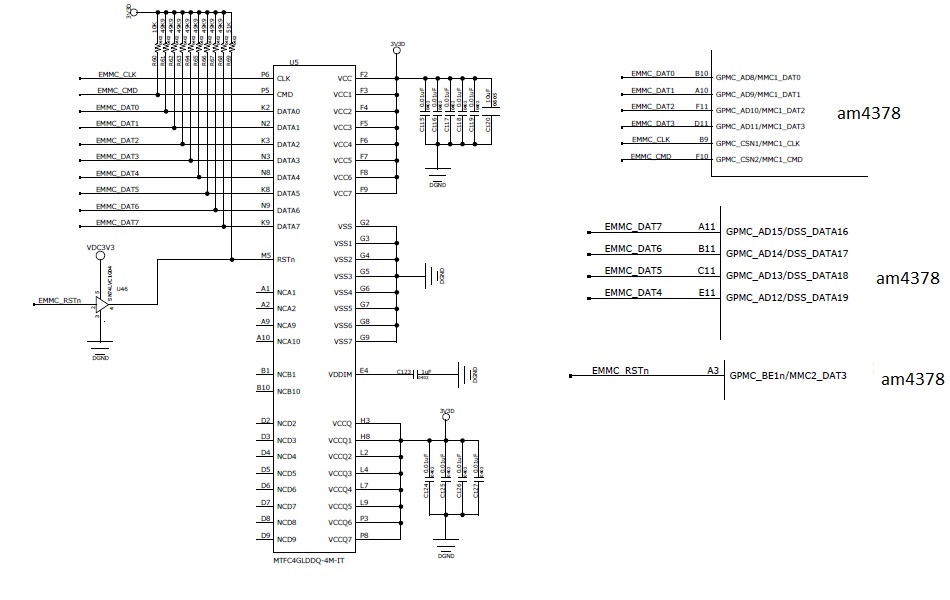

My schematic is as follows

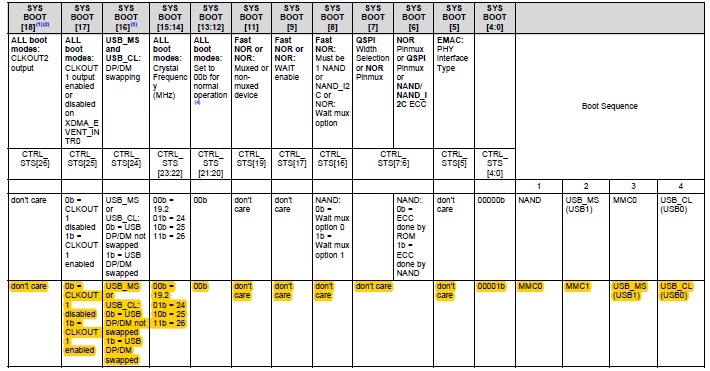

My boot sequence given below.

I am following the below link to update files and boot from eMMC,

I enter the following command from uboot,

U-Boot # printenv partitions

uuid_disk=${uuid_gpt_disk};name=rootfs,start=2MiB,size=-,uuid=${uuid_gpt_rootfs}

U-Boot # setenv uuid_gpt_disk ...first uuid...

U-Boot # setenv uuid_gpt_rootfs ...second uuid...

U-Boot # gpt write mmc 1 ${partitions}

When i enter "U-Boot # gpt write mmc 1 ${partitions} " , I got below error,

"Card did not respond to voltage select!

do_gpt: mmc dev 1 NOT available "

What could be the reason? How do i solve this problem?

Regards,

Winiston.P