Hi,

I have qestion about EMIF timing of C5517.

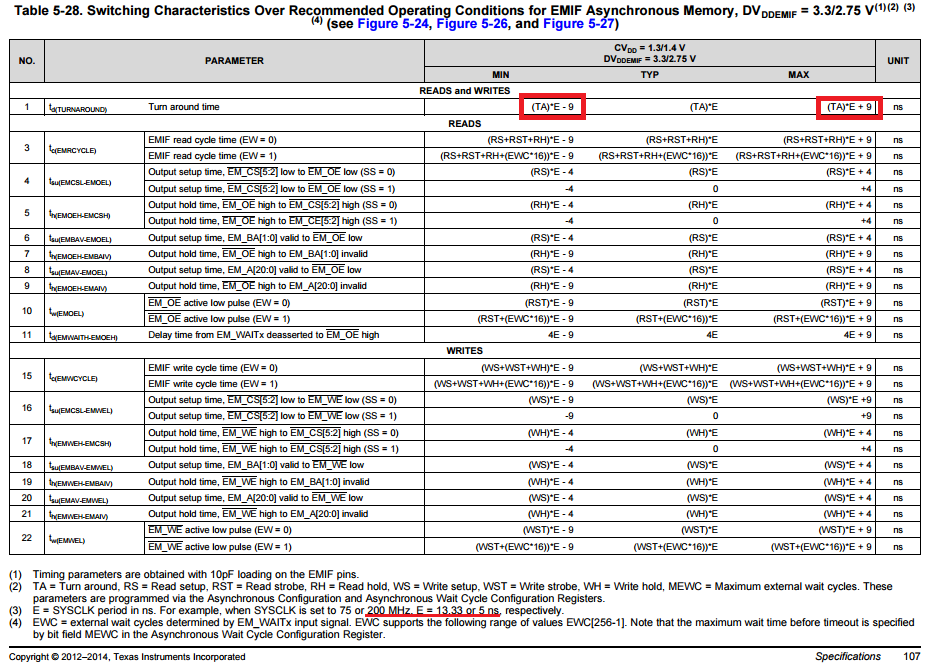

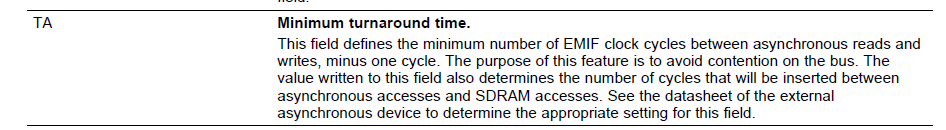

The td(TURNAROUND) is described as follows.

If SYSCLK is used at 200 Mhz, the minimum value will be a negative value, so I think that this prescribed value is wrong.

Is the margin (± 9 ns) incorrect?

Best regards,

H.U