Hi,

I have sample application which runs OK from either IRAM and DDR2 when using JTAG.

When I program the two versions (IRAM and DDR2) to a parallel NOR flash, the IRAM version runs OK, but the DDR2 fails.

My conclusion is that the AISgen fails to initialize the DDR2.

The C6748 runs at 300MHz, the DDR2 runs at 150MHz (top speed of the DSP's DDR controller).

Any idea what I did wrong?

Regards,

Uri

This is the GEL section for the DDR2 (known to work OK):

DEVICE_mDDRConfig(unsigned int freq) {

int i;

#define DRPYC1R (DDRCTL)

#define SDCR2_BOOTUNLOCK (0x00800000)

#define SDCR2_TIMUNLOCK (0x00008000)

GEL_TextOut("\tDEVICE_mDDRConfig %d MHz","Output",1,1,1, freq);

/* 2.13.2 [1] */

// Done @ device_PLL1()

/* 2.13.2 [2] */

// Enable the Clock to EMIF3A SDRAM/DDR

PSC1_LPSC_enable(PD0, LPSC_DDR);

/* 2.13.2 [3] */

// VTP IO calibration

#define VTP_CLKRZ (0x00002000)

#define VTP_LOCK (0x00000080)

#define VTP_POWERDN (0x00000040)

#define VTP_READY (0x00008000)

#define VTP_IOPWRDN (0x00004000)

VTPIO_CTL &= ~( VTP_CLKRZ | VTP_LOCK | VTP_POWERDN ); // a

for (i = 0; i++; i<10) {} // a

VTPIO_CTL |= VTP_CLKRZ; // b

while(!((VTPIO_CTL & VTP_READY) >> 15)) {} // c

VTPIO_CTL |= VTP_IOPWRDN; // d

VTPIO_CTL |= VTP_LOCK; // e

VTPIO_CTL |= VTP_POWERDN; // f

GEL_TextOut("\tVTP calibration completed","Output",1,1,1);

/* 2.13.2 [4] */

// DDR PHY control register 1

DRPYC1R = 0x84; // EXT_STRBEN = External strobe. RL = (CAS latency + 1)

/* 2.13.2 [7] */

/* 2.13.1 [7 2] */

// Program the SDRAM configuration register (SDCR) with BOOTUNLOCK bit set to 1 (unlocked).

EMIF3A_SDCR |= SDCR2_BOOTUNLOCK;

EMIF3A_SDCR |= SDCR2_TIMUNLOCK;

/* 2.13.1 [7 3] */

EMIF3A_SDCR = 0x0093C622; // BOOTUNLOCK locked

EMIF3A_SDCR &= ~(SDCR2_BOOTUNLOCK); // BOOTUNLOCK locked

/* 2.13.1 [7 4] */

// SDCR2

EMIF3A_SDCR2 = 0x00000004; // 8K rows

/* 2.13.1 [7 5] */

// Timers

EMIF3A_SDTIMR1 = 0x1E922A09;

EMIF3A_SDTIMR2 = 0x8412C722;

/* 2.13.1 [7 6] */

// TIMUNLOCK locked

EMIF3A_SDCR &= ~(SDCR2_TIMUNLOCK);

/* 2.13.1 [7 7] */

// Refresh rate

EMIF3A_SDRCR = 0x00000249 | (0x1 << 30) | (0x1 << 31); /* The two MSB bits are per correction from the forum */

/* 2.13.2 [5] */

// PSC reset

PSC1_LPSC_SyncReset(PD0, LPSC_DDR);

PSC1_LPSC_enable(PD0, LPSC_DDR);

/* 2.13.2 [6] */

// 00h will ensure master priority is strictly honored (at the cost of decreased

// DDR2/mDDR memory controller efficiency)

EMIF3A_PBBPR = 0x20;

}

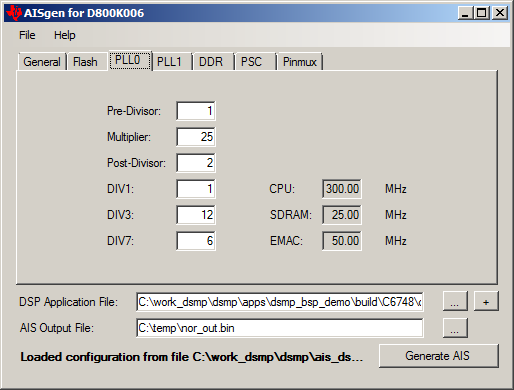

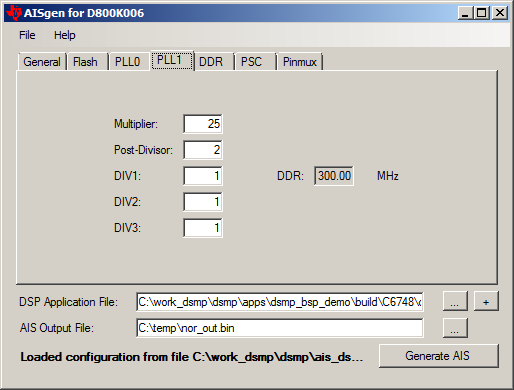

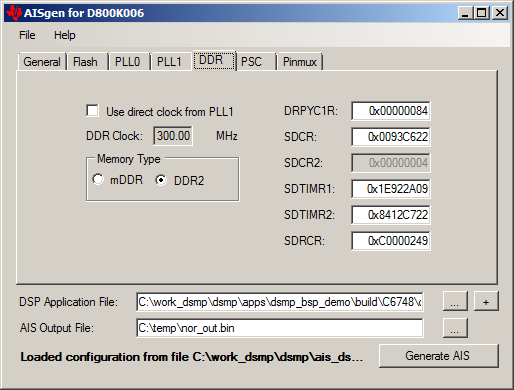

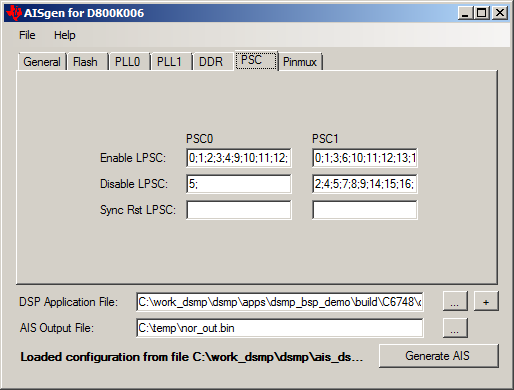

The AISgen configuration is: