Hello,

I currently develop a BOOT software on a DSP TMS320C6678. This software is loaded in a FLSAH NOR SPI.

I’m testing the BOOTLOADER (RBL) to load this software in RAM after a DSP reset.

Test is done using TRACE32 and a LAUTERBACH probe.

Hereafter the Test protocol :

- The DSP is configured in Little Endian (LSB of DEVSTAT register set to 1).

- The Boot Parameter Table is generated in Big Endian Format.

- Run of a .cmm file which sets the Program Counter to the entry point of the BOOTLOADER (@0x20B0FC00)

- Set the DEVSTAT register (@0x02620020) to 0x0000260D value, meaning SPI BOOT mode and Boot Parameter Table at the beginning of the FLASH SPI

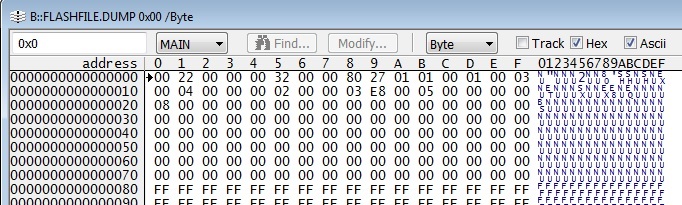

Boot Parameter Table in SPI :

- Run again the same .cmm file

Question 1 : Is this test protocol correct ? Currently, I haven’t implemented the solution to set the

GPIOs used for the Boot Mode configuration in the correct state.

Hereafter what occurs :

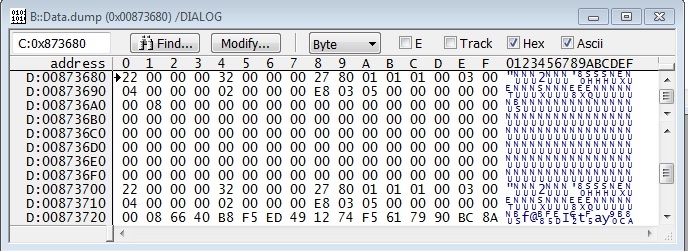

- The Boot Parameter Table is copied in RAM at @ 0x00873680 which is the memorization address in RAM by the BOOTLOADER :

The memorization seems correct considering the BOOTLOADER works in Little Endian.

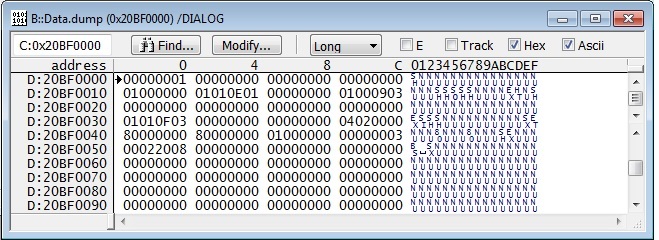

- Hereafter the resulting SPI registers configuration :

The resulting configuration doesn’t correspond exactly to the wanted one :

-

- wanted C2Delay is 0. In the dedicated SPI register, C2Delay is set to 1.

- SPI is not in MASTER mode and not ENABLED

Except to those points, Configuration is available with the used FLASH NOR.

Question 2 : what’s wrong in my configuration (Note that Main PLL is wanted to 1 Ghz) ?

In fact, I wonder if the Boot Parameter Table present in RAM is not a Boot Parameter Table by default !!!

Question 3 : Shall the Boot Parameter Table be generated in Little Endian format ?

I have already done the associated test.

The Boot Parameter Table is not correctly memorized at @ 0x00873680 … content of this zone is quite different of the real Boot Parameter Table

But in this case, SPI is in MASTER mode, ENABLED and Chip Select is in HOLD state

In all cases, the Boot Table is not copied in RAM or at an unknown location in RAM.

Note that Boot Table is generated using successively hex6x, bconvert64x and b2i2c.

Boot Table in FLASH SPI is set at @0x0800.

Without any more informations, I can"t investigate any more. Thanks a lot for your future answer

Regards

Alban