Other Parts Discussed in Thread: SYSBIOS

Tool/software: TI-RTOS

Hello,

I am using a custom K2L board for transferring 16-bit data from a CPLD through EMIF-16 to DDR3 memory using EDMA3, My problem is that the either the EDMA or the DMA completion interrupt needs some "waking up" until it begins working at full speed.

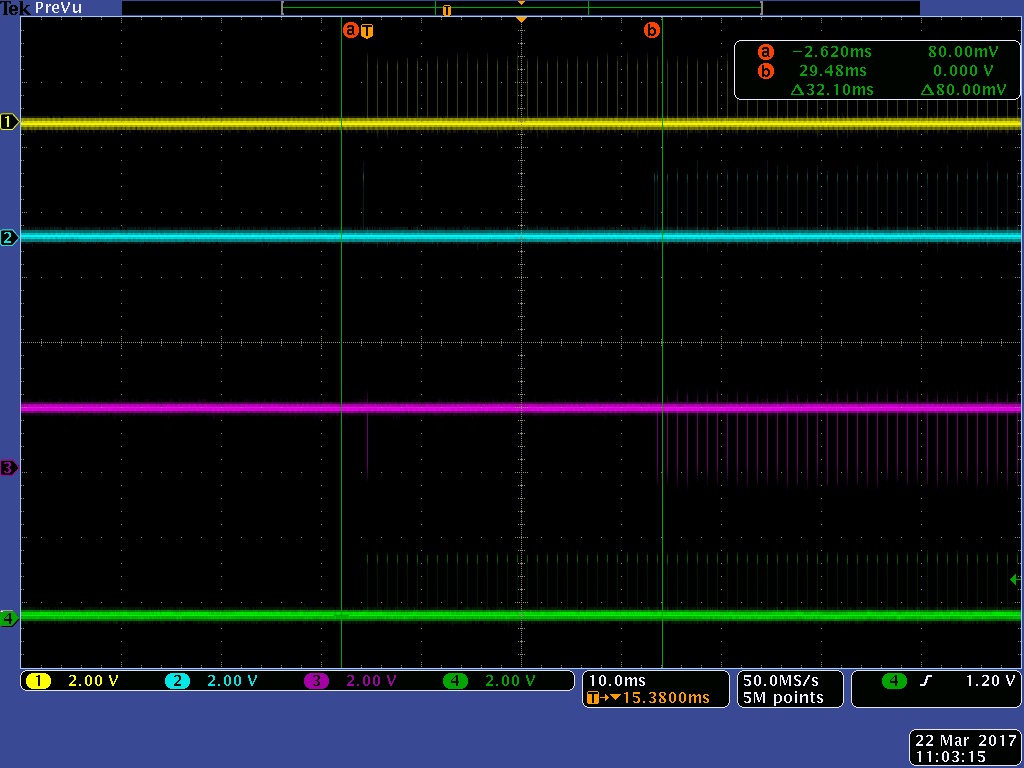

Everything seems good except for the EDMA sleeps 30 msec in the beginning of the transfers. See the oscilloscope figure below:

The yellow signal shows the events (GPIO 10) from the CPLD to the C66 DSP CPU.

The blue signal (GPIO 9) shows when the DMA completion interrupt is executed.

The purple signal is EMIF read signal.

The green signal is used for activating the CPLD for doing its job which in turn results the yellow signal out of the CPLD.

The figure shows that the CPLD wakes up immediately when the C66 DSP CPU enables the green signal, AND the EDMA makes one read from the EMIF-16. Then it stops working for 30 msec.. Why??? After waking up it does not sleep any more. It can continue working just fine for hours.

Before enabling the green signal the EDMA and its interrupts have been configured and they are not modified after that any more. There is nothing special to happen after enabling the green signal, and the same transfer should continue forever until the green signal is finally disabled by the CPU.

DMA PaRAMs

OPT: 0x80112004

SRC: 0x34000080

AB-CNT: 0x000C0002

DST: 0xA0000180

BIDX: 0x00200040

LINK-RELOAD: 0xFFFF0000

CIDX: 0x00020000

C-CNT: 0x00000010

The DMA completion fires an interrupt which updates the destination address and re-enables the transfer. Each event makes 12 16-bit data transfers and this is repeated 16 times per each green signal pulse. This is not visible (pulses are too close to each other on the screen) in the oscilloscope figure above, but I have verified by looking more closely that this works alright.

I have tried to adjust the HWI interrupt priorities and SYS/BIOS task priorities, but they don't help. There are no other interrupts active which could preempt the EDMA completion ISR. I have also tried removing the EDMA event missed interrupt and the CC error interrupt. No effect.

I have tried with giving the events in different frequencies: 100Hz, 300Hz, 1kHz, 10kHz and 40 kHz. The sleep time is always the same: 30 msec.

I set up the tasks and interrupts like this in the code:

Main task which makes all the settings for the EDMA (uses EDMA3 LLD, driver from TI), GPIO, CPLD and the EDMA3 interrupts (completion, event missed, cc error).

stackSize = 0x2000;

priority = 0; // originally 5

Idle loop which runs all the non time critical functions. Currently it is empty doing nothing. Originally it was included in the main task as a never ending while-loop.

Idle.idleFxns[0] = "&mainTask";

The EDMA completion interrupt is an HWI task having automatically the highest priority level, right? I setup the interrupt like this:

CpIntc_dispatchPlug(40, isr_handler, 0, TRUE);

CpIntc_mapSysIntToHostInt(0, 40, 68);

CpIntc_enableHostInt(0, 68);

EventCombiner_dispatchPlug(26, (ti_sysbios_family_c64p_EventCombiner_FuncPtr)CpIntc_dispatch, 68, TRUE);

EventCombiner_enableEvent(26);

40 = CIC0 EDMACC_0_TC_2_INT, the EDMA event 18 (GPIO 10) is assigned to this in the "ccXferCompInt" array included in the EDMA3 LLD package.

26 = C66 CorePac primary interrupt CIC_OUT68_PLUS_10_MUL_N

The "isr_handler" function (in pseudo language):

isr_handler(const EDMA3_RM_Obj *rmObj)

{

SET GPIO 9 to "1" this is visible in the oscilloscope (blue signal)

while (IPR & (1 << 18)) {

ICR = (1 << 18);

}

EESR = (1 << 18);

UPDATE DMA DESTINATION

PREPARE EDMA FOR NEXT EVENTS

SET GPIO 9 to "0" this is visible in the oscilloscope (blue signal)

}

Versions of the used tools:

Compiler: TI v7.4.16

CCS: v6.1.1

XDCtools: 3.30.5.60

SYS/BIOS: 6.45.1.29 [6.42.2.29] <-- does this mean the project was originally built with a newer version, but this PC has only 6.42.2.29 installed on it? Can this have some effects like this?

IPC: 3.35.01.07

PDK: 3.01.03.06

EDMA3 LLD: 02.11.13.17

Is this a bug in the configuration I have made, or is this a bug in the SYS/BIOS or in the EDMA controller itself?

Best regards,

Ari