Part Number: TMS320C6678

Hello,

I`m trying to understand exact way for SRIO booting on C6678. I read bootloader user guide and my current understanding is below:

- User`s application code for SRIO booting can`t use RBL`s work area for any 'initialized section'. But user can still put 'uninitialized section' on that area.

- If users want to use DirectIO mode for SRIO booting, the host must know DSP`s memory map exactly. Host must write required memory image into target device memory space via SRIO direct IO.

- Once required image has been written, host must write address information for entry point (in most case, c_int00) into MAGIC address. During SRIO booting, RBL keeps polling MAGIC address and branches to it once it is non-zero value. And then, application starts its execution (on core0)

First of all, please let me confirm my understanding is correct.

And the following is my questions;

1. Bootloader user guide says there is 32KB for RBL workspace, but i can`t understand exact address.

2. I`m now reading BootROM_C6678_PG2.0\BootROM_c6678_PG2.0\main\riomain2.c for my understanding. I believe the following is core loop for waiting MAGIC.

do {

/*--------------------- SRIO direct write boot mode processing ------------------ */

#ifdef BOOTCONFIG_INCLUDE_RAPIDIO_BTBL

if ((origOptions & BOOT_PARAMS_RIO_OPTIONS_BOOT_TABLE) == 0) {

#endif

/* */

/* */

/* */

/* */

/* */

} else {

/* Wait for the rapid I/O interrupt */

chipSleepUntilEvent ((UINT16)DEVICE_SLEEP_RIO_EVENT);

}

/* Clean up after the rio interrupt */

hwRioCleanup ();

/* Peform any table processing (emif config tables, peripheral config tables, etc) */

chipRioBlockDone ();

#ifdef BOOTCONFIG_INCLUDE_RAPIDIO_BTBL

/*------------------- SRIO message mode (boot table) processing --------------------- */

} else {

/* In case direct write boot is used with the boot table bit set (the default),

* poll the ifr bit. If set check to see if DDR setup was setup */

if (chipPollIfr (params->portNum, DEVICE_SLEEP_RIO_EVENT) == TRUE) {

hwRioCleanup ();

chipRioBlockDone ();

}

pkt = chipSrioGetPkt(&vcppi, &len);

if (vcppi != NULL) {

status = boot_rio_table_proc (pkt, len);

if (chipSrioPktDone (vcppi) != 0) {

bootStats.u.rapidIo.rapidIoDescrEmpty += 1;

chipStatusRioDescrEmpty();

}

if (status == RIOMEM_LENGTH_READY_LENGTH_INVALID) {

bootStats.u.rapidIo.rapidIoBtblBadBlocks += 1;

chipStatusRioBadLength ();

} else if (status == RIOMEM_LENGTH_READY_CHKSUM_FAIL) {

bootStats.u.rapidIo.rapidIoBtblBadBlocks += 1;

chipStatusRioBadChksum ();

} else {

bootStats.u.rapidIo.rapidIoBtblBlocks += 1;

chipStatusRioBtbl ();

}

/* Peform any table processing (emif config tables, peripheral config tables, etc) */

chipRioBlockDone ();

}

}

#endif

} while ( !(*p_boot_entry_addr) );

Now no definition for BOOTCONFIG_INCLUDE_RAPIDIO_BTBL, so most of the code is not activated in RBL. so now it should look like this :

do {

/*--------------------- SRIO direct write boot mode processing ------------------ */

/* */

/* */

/* */

/* */

/* */

} else {

/* Wait for the rapid I/O interrupt */

chipSleepUntilEvent ((UINT16)DEVICE_SLEEP_RIO_EVENT);

}

/* Clean up after the rio interrupt */

hwRioCleanup ();

/* Peform any table processing (emif config tables, peripheral config tables, etc) */

chipRioBlockDone ();

} while ( !(*p_boot_entry_addr) );

...As you see, c-scope is inconsistent. Can you share the corrected do-while for my reference ?

Sorry, I don`t know exact SRIO specification ... so my poor question starts from here :-(

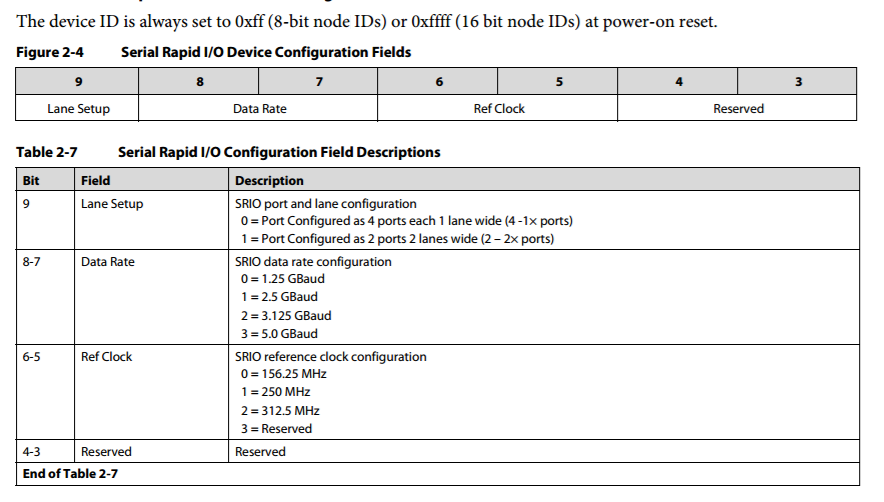

3. If I understand RBL code correctly, during RBL process, the node id (device id ?) seems to be 0xFFFF by default. Does this mean DSP can accept any incoming packets having any destination id ?

4. If SRIO switch is present between HOST and DSPs, how does host select target DSPs (having same node id as 0xFFFF) for downloading the image ? If host configures SRIO switch to route the packet to dedicated output port for a target DSP, and send packets with any device ID, the slave DSP can accept incoming packets ?

5. If a single application image is running on core0-7, how to run core1-7 after SRIO booting ? Let`s assume all cores are sharing the code on MSMC SRAM and some local sections dedicated for each core are present on L2 local address. In this case, I`m wondering if the following scheme can work for me. Is that correct ?

- Host is holding DSP boot table image. Host downloads each sections into DSP via SRIO DirectIO by parsing boot table format. During this process, it can detect initialized sections dedicated for L2 local address and host can convert them from LOCAL to GLOBAL address and download them for ALL cores. As for shared sections on MSMC SRAM, host just download it as is. After boot process is completed successfully, only core0 application starts working and it has to generate IPC interrupts for each of the secondary CorePacs to awake. Then secondary cores (core1-7) starts their execution.

Sorry for many poor questions but I have some customers to use SRIO booting , so I want to exact way. It would be appreciated if you could answer to my questions. Thank you !!

Best Regards,

Naoki