Part Number: TMS320C6424

Hi TI

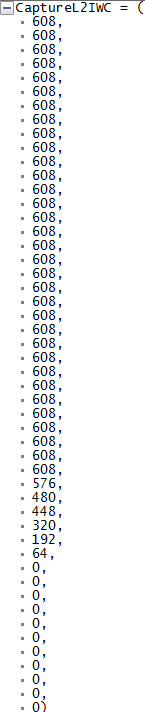

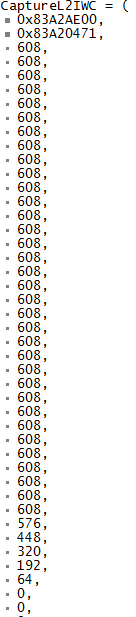

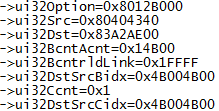

I have a EDMA memory transfer from one memory location to another both in external memory. Size is about 19 kB. I use cache invalidation to ensure the cache is flushed, but tests have shown that some of the memory isn't flushed.

Here is what I do:

1) memset(&stDataFile[ui8DataFileIndex].stData, 0, sizeof(stDataFile[ui8DataFileIndex].stData));

2) BCACHE_wbInv(&stDataFile[ui8DataFileIndex].stData, sizeof(&stDataFile[ui8DataFileIndex].stData), TRUE);

3) Initaite EDMA transfer

4) wait for EDMA transfer to complete by checking bit in IprH register

5) BCACHE_inv(&stDataFile[ui8DataFileIndex].stData, sizeof(stDataFile[ui8DataFileIndex].stData), TRUE);

If I check the data right after step 5, there is random ranges in the memory with the value 0 (from the memset in step 1).

If I wait a couple of ms (TSK_sleep) or longer the data is correct.

Any suggestions of what might cause this?