Part Number: Dra750

Tool/software: Linux

Hi all,

we are using DRA7xx_GLSDK_7.04.00.03 to develop our custom board.

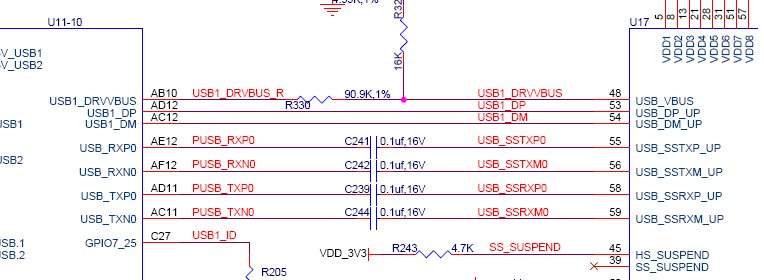

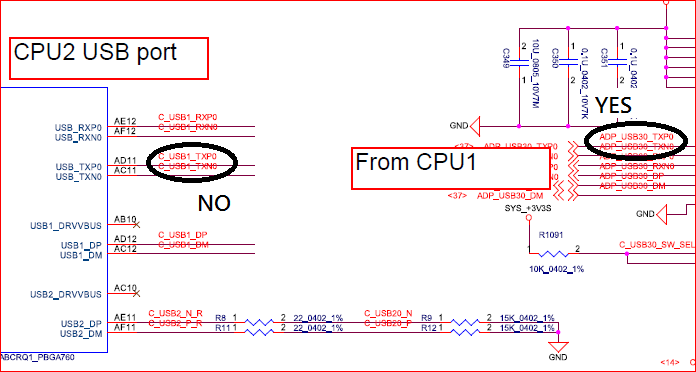

We have two custom board using dra750 as CPU, and connect their usb1(3.0 port) together.

One is setting to host mode, while the other is setting to device mode.

When we modeprobe g_mass_storage.ko on the device one,

Host will detect a mass storage: /dev/sda,

(refer to: processors.wiki.ti.com/.../Linux_Core_DWC3_User's_Guide)

Then we partition and formate /dev/sda and mount it to a directory.

Finally we use dd command to create a file in that directory.

The problem is that it seems operating in high speed mode, not super speed.

How to make it to work in super speed or any setting can force both usb1 ports to work in super speed?

Pleas kindly give me some advice, thank you so much.