Part Number: AM5728

Other Parts Discussed in Thread: AM5718

Hi,

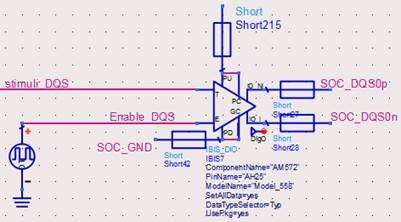

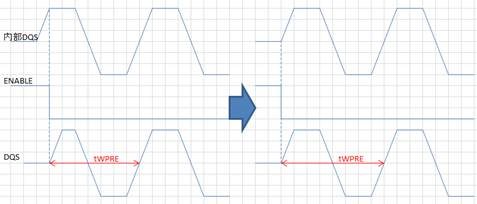

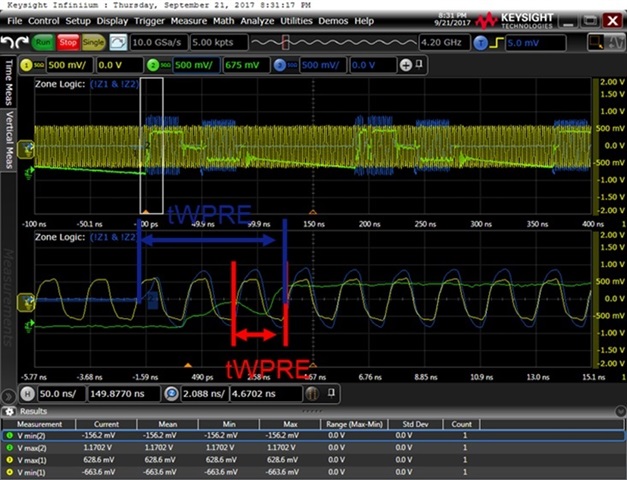

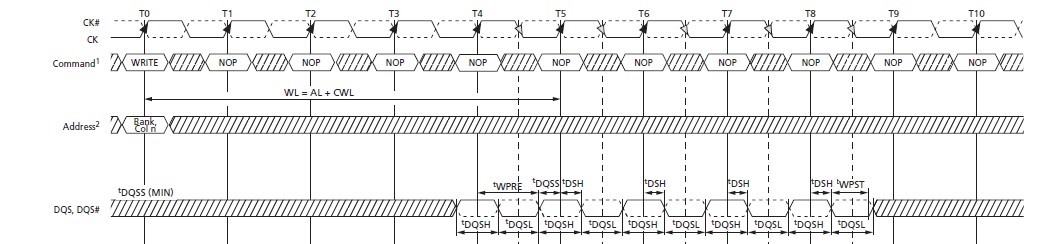

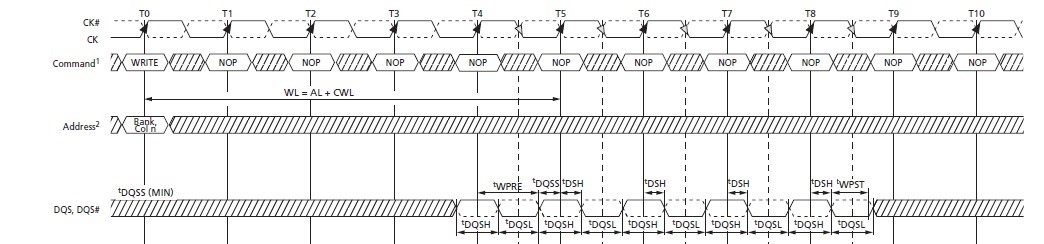

Our customer fails in a timing of tWPRE of DDR3 compliance test of AM572x.

A start of DQS of the tWPRE section is late, and it does not satisfy min of tWPRE(0.9*tck).

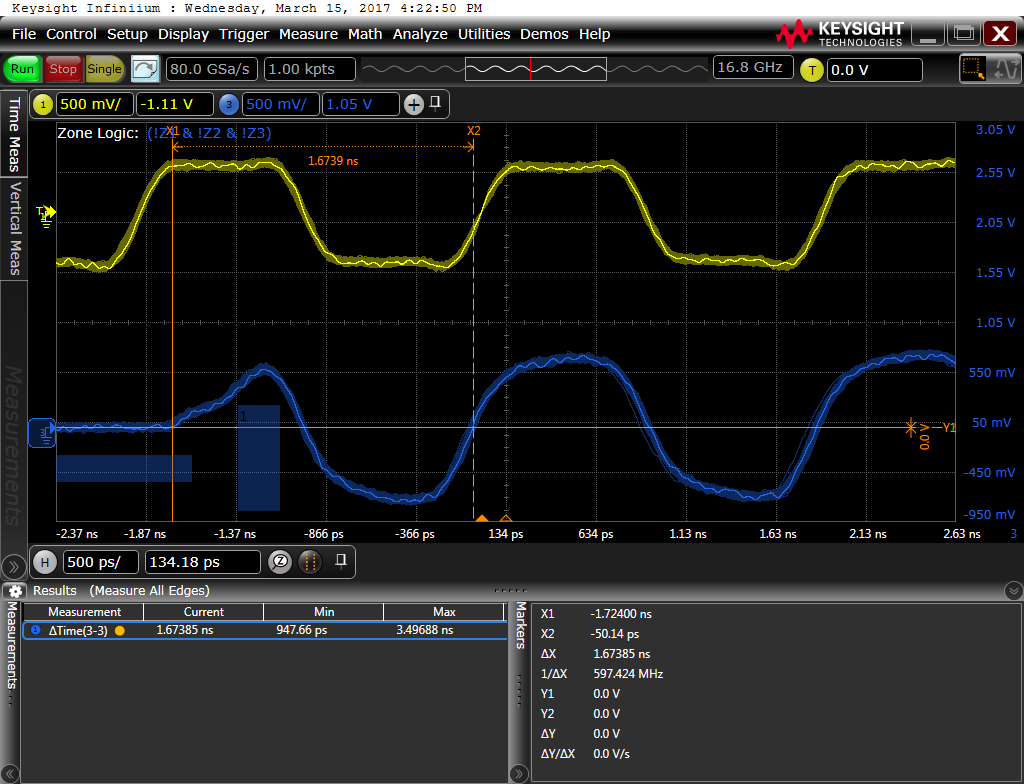

Please confirm the following wave pattern.

Yellow: CK signal

Blue: DQS signal

The following countermeasures were taken, but in both cases the timing of tWPRE did not satisfy spec.

1.A change of DDR_TERM bit

2.A change of SDRAM_DRIVE bit

3.The change of PHY_INVERT_CLKOUT bit and the PHY_REG_CTRL_SLAVE_RATIO0 bit

4.The change of the DDR3CH2_PART6_I[7:5] bit of the CTRL_CORE_CONTROL_DDRCACH2_0 register

5.The change of the DDRCH2_PART4B_I[7:5] bit of the CTRL_CORE_CONTROL_DDRCH2_1 register

6.The change of the DDRCH2_PART4B_I[7:5] bit of the CTRL_CORE_CONTROL_DDRCH2_1 register

7.I change terminal resistance of the CK into 51 Ω from 39 Ω.

There are two questions.

1.How can we do to increase the tWPRE section of DQS or to speed up the rise time of tWPRE?

Please tell me how to do it.

2.Does the problem that tWPRE timing does not meet spec in other users using AM572x not occur?

Best Regards,

Shigehiro Tsuda