Tool/software: Linux

Hi

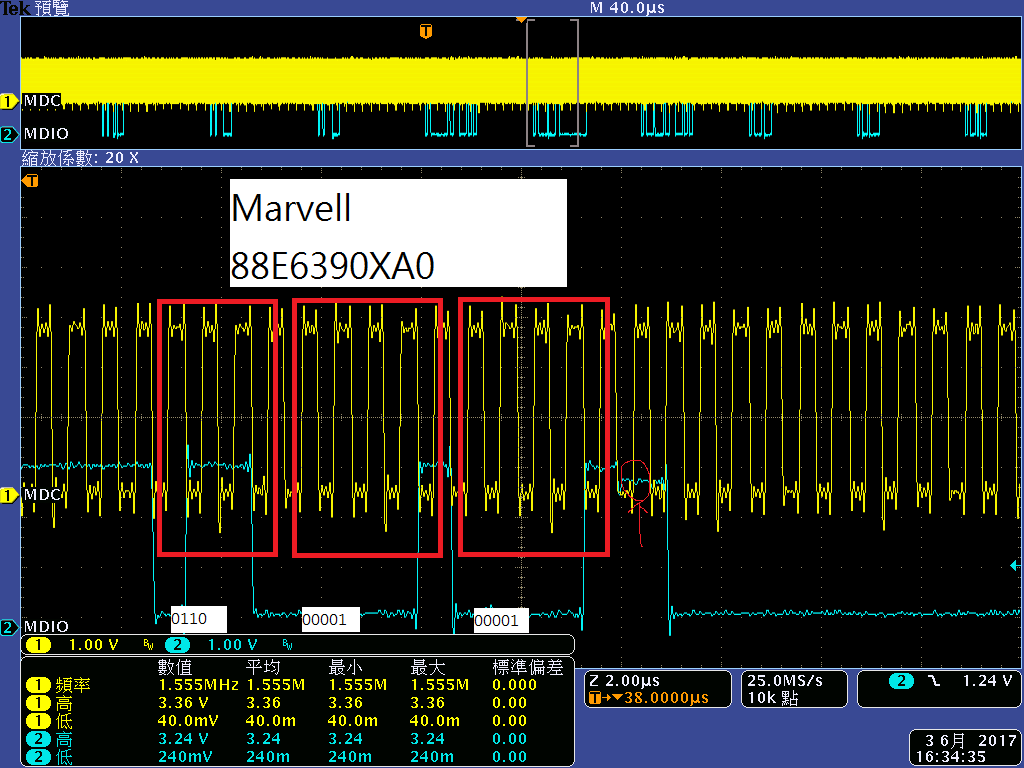

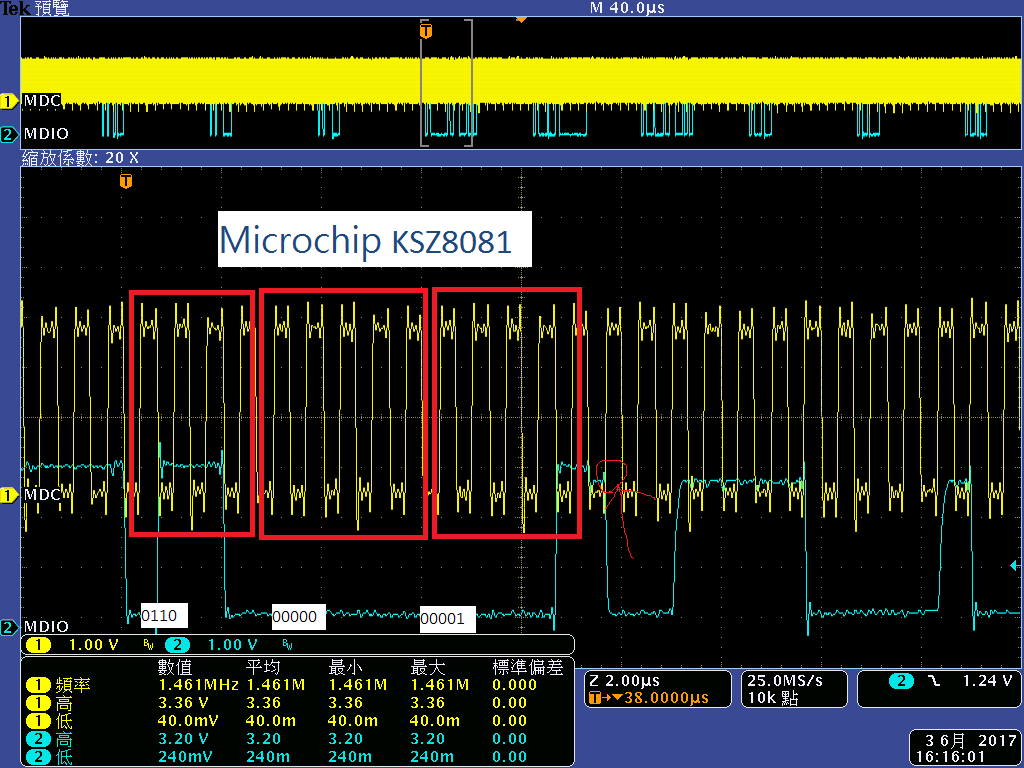

I do connect two Ethernet device Microchip KSZ8081 and Marvell 88E6390XA0 together with MDIO/MDC of DRA744.

I can get KSZ8081 device information by mdio read command, but 88E6390XA0 just return error.

We also call help to Marvell FAE that FAE can get 88E6390XA0 device information with his fixture tool.

Then I try to measure the wave find the difference between KSZ8081 and 88E6390XA0.

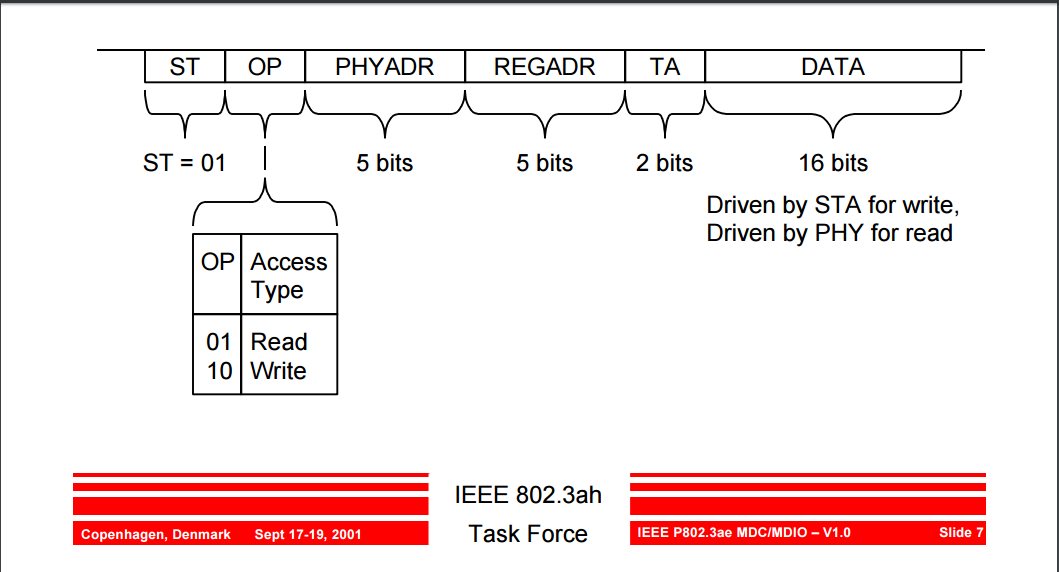

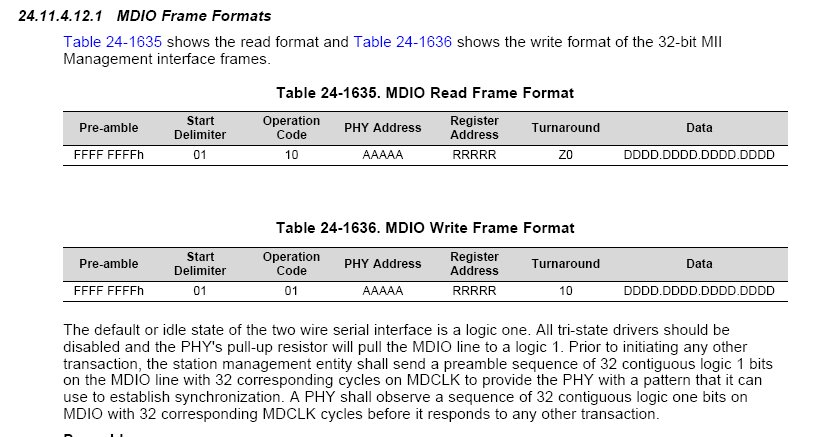

After DRA744 was sent the register address, 88E6390XA0 has additional one high bit. as below picture.

Do any register setting can cover this difference?

thank you