Other Parts Discussed in Thread: TIDEP0014,

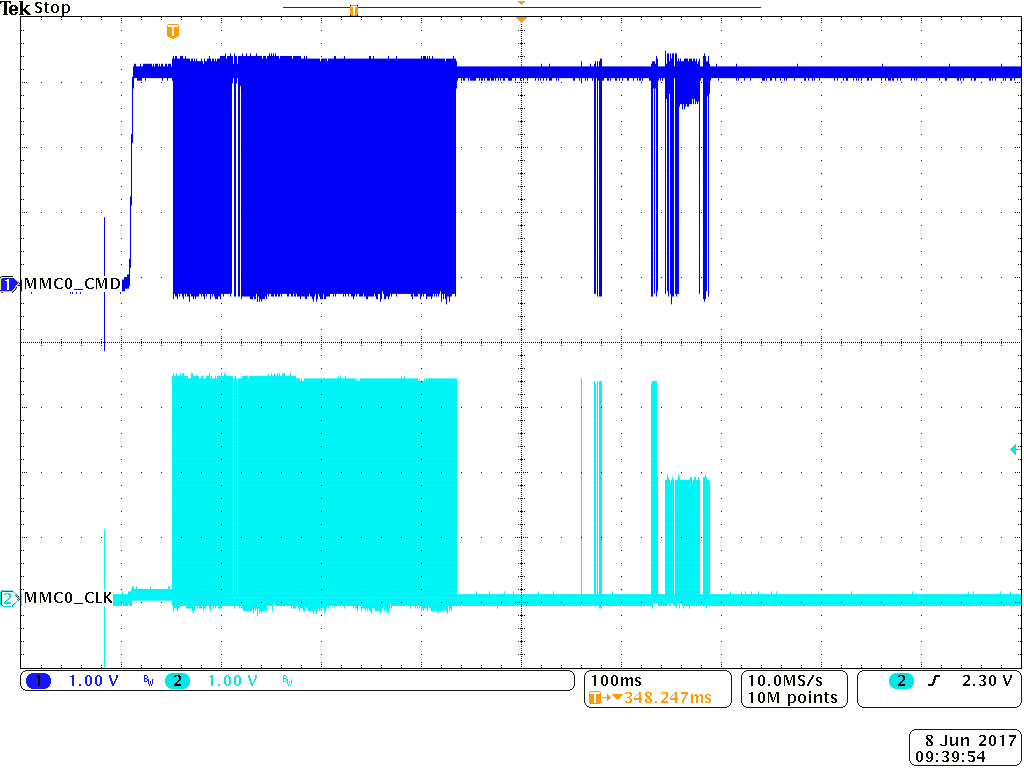

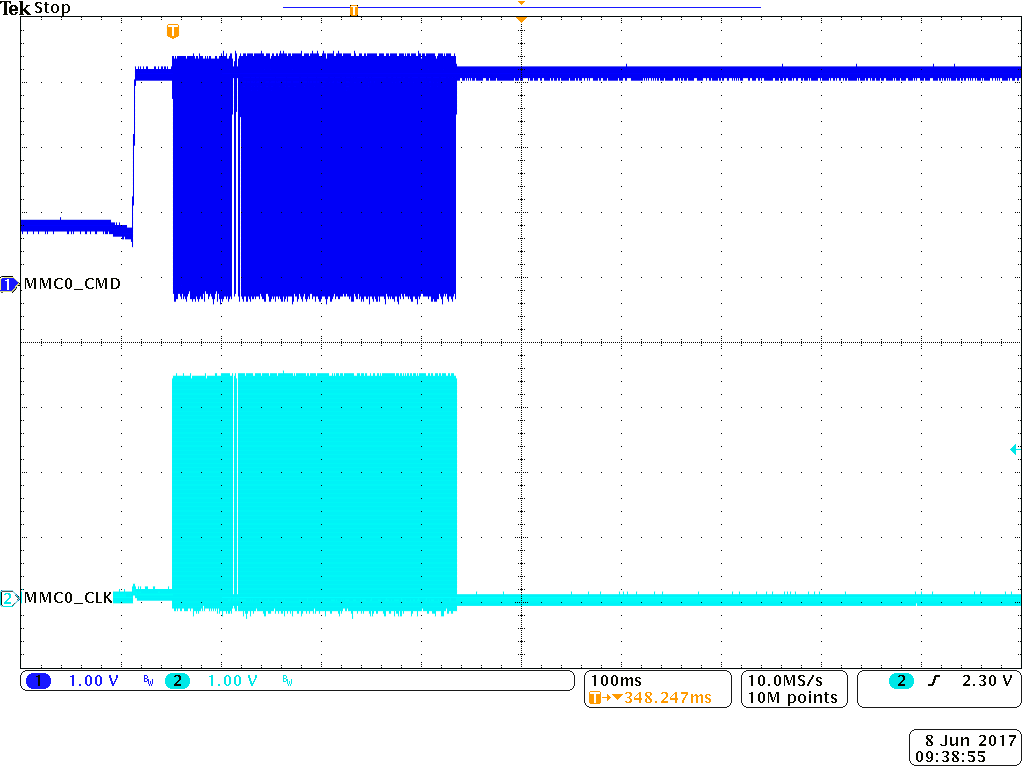

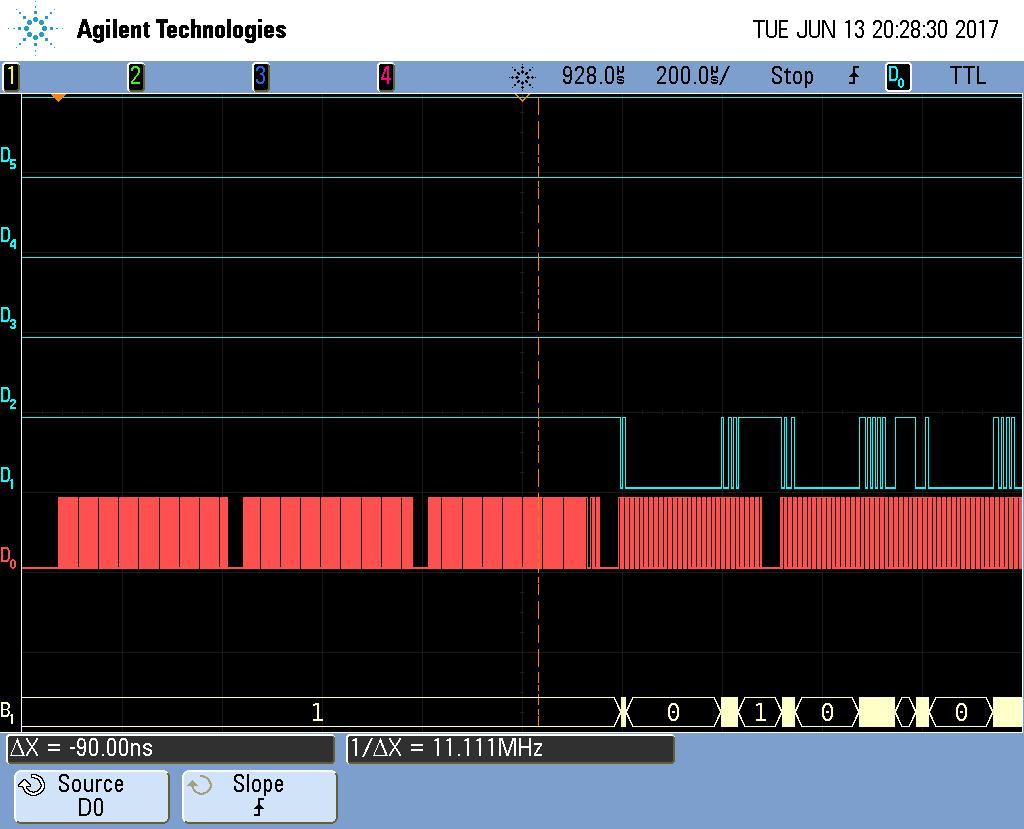

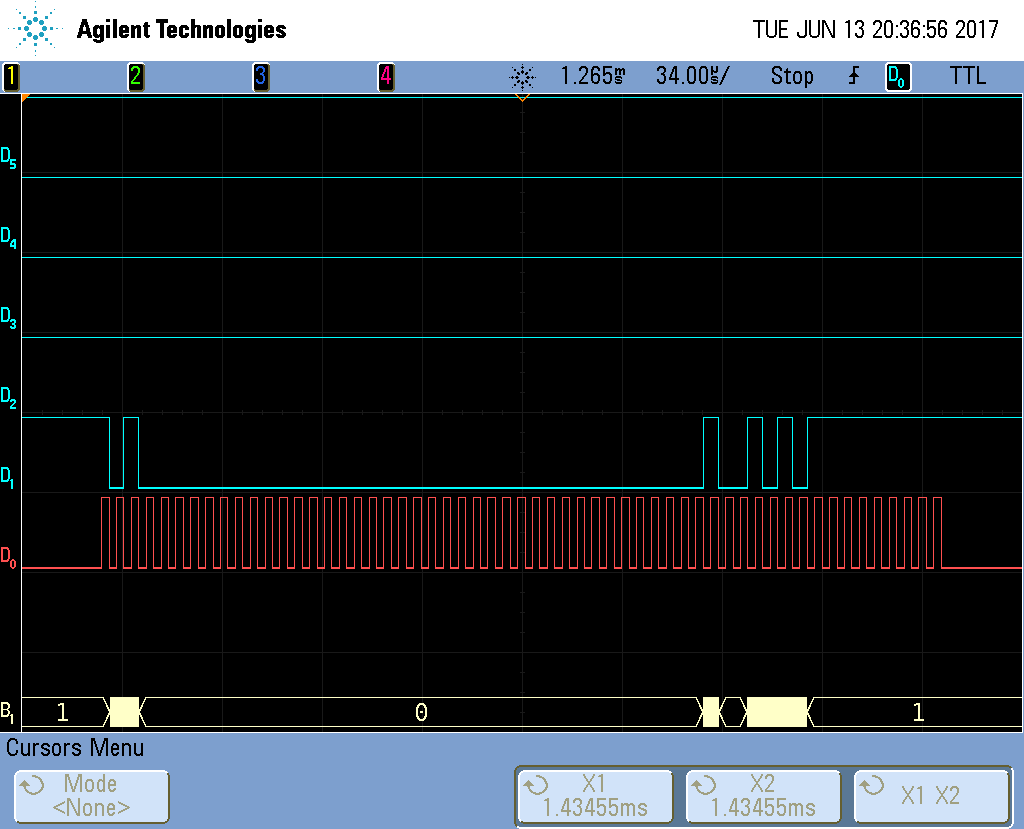

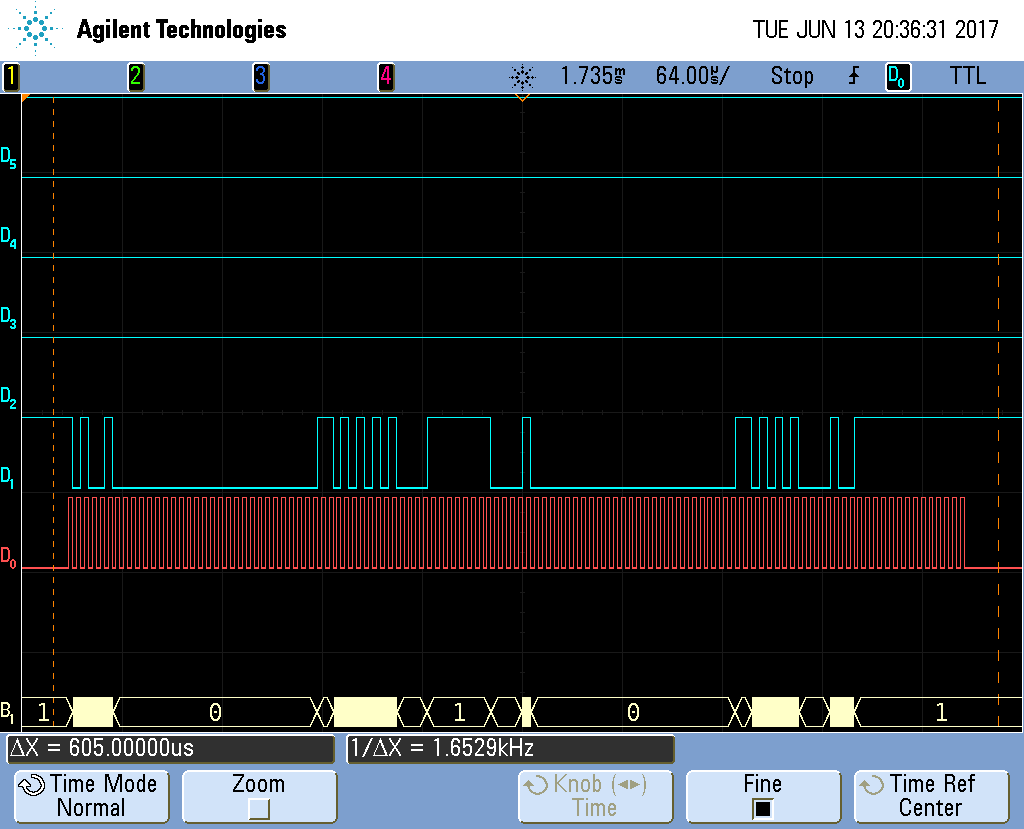

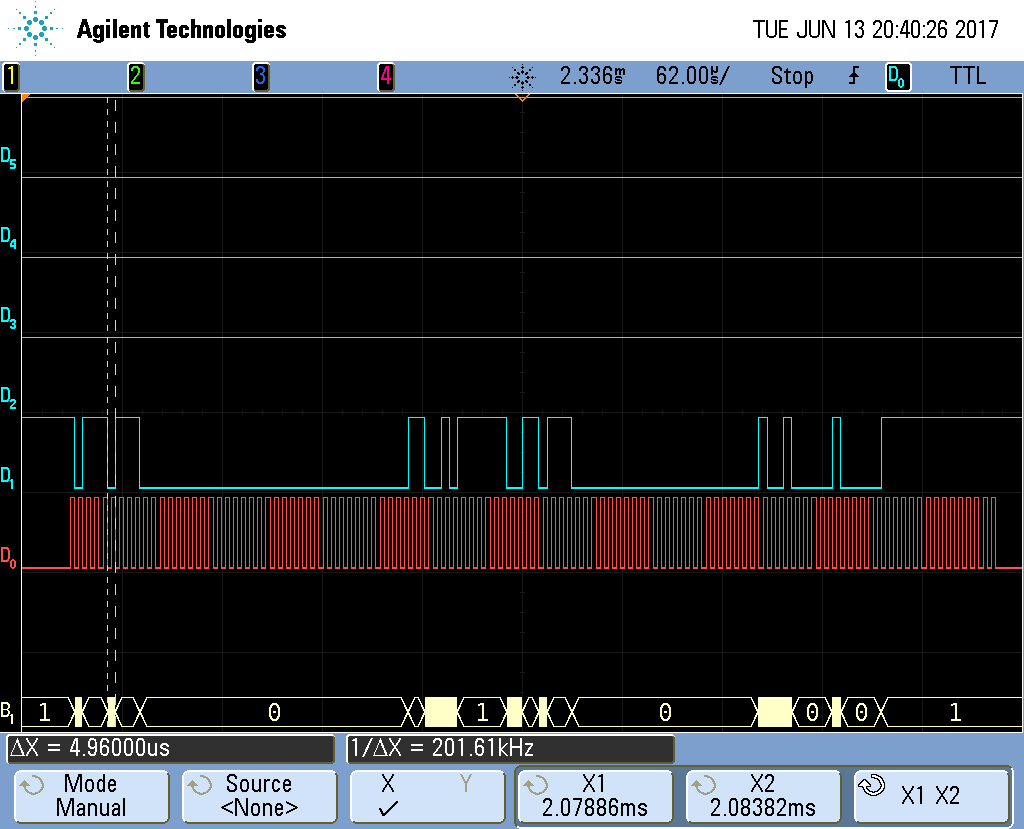

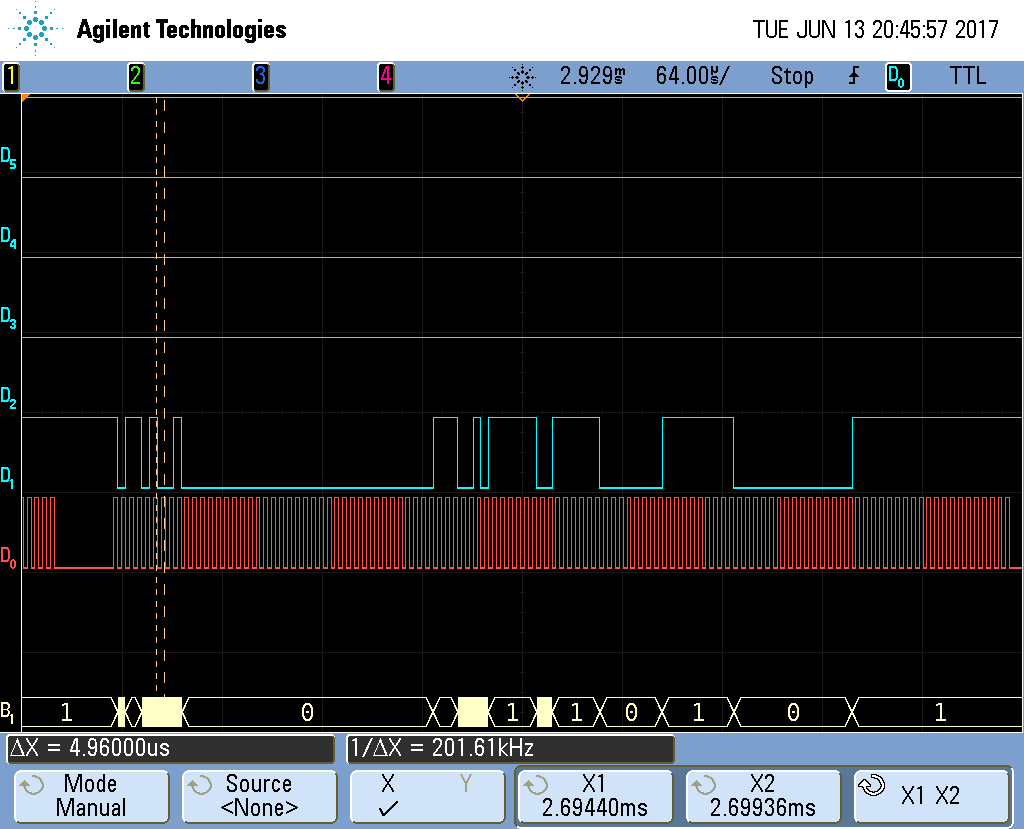

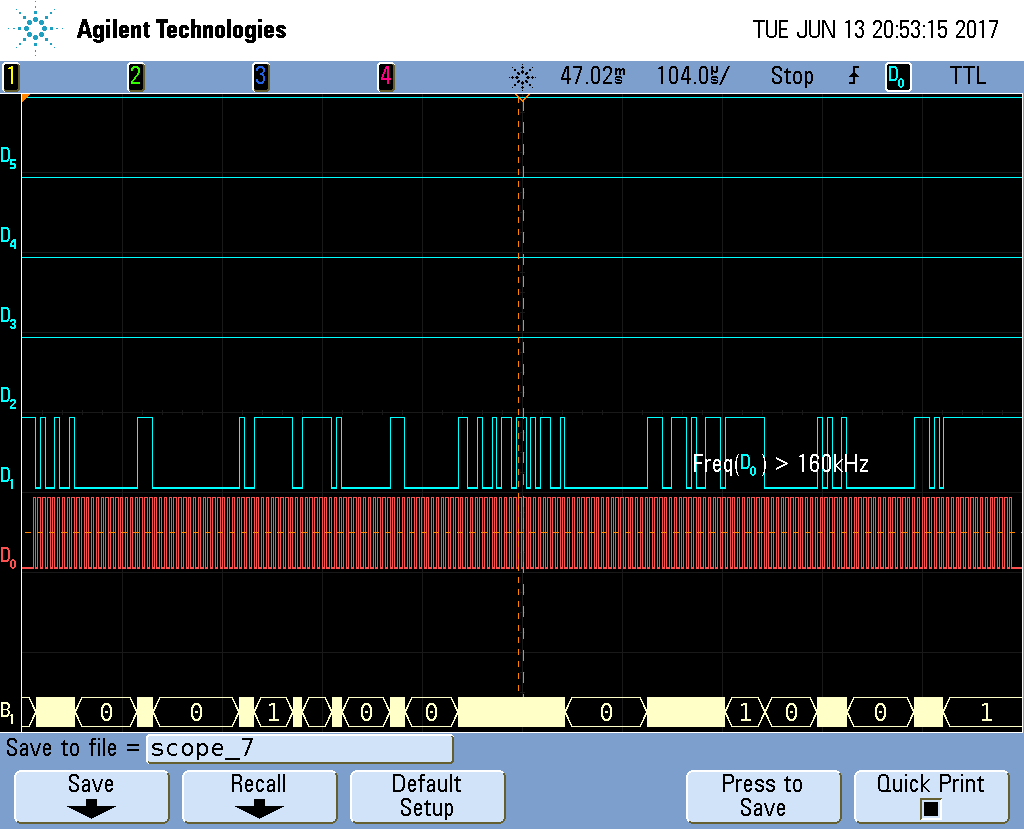

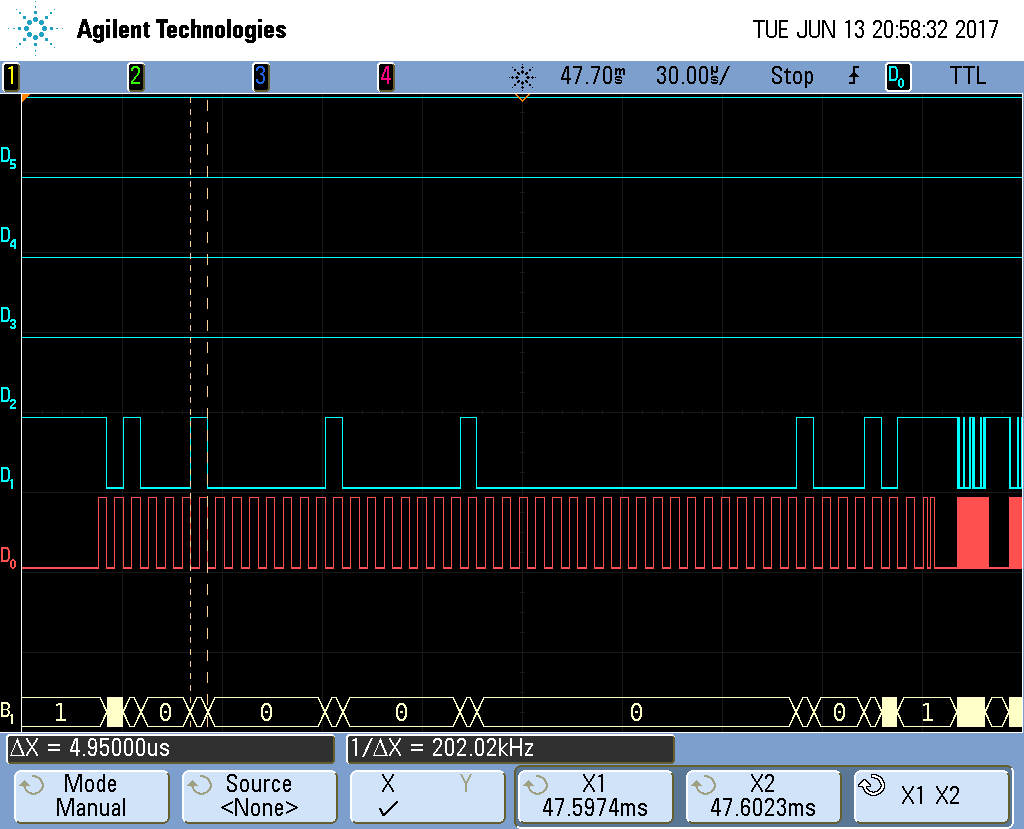

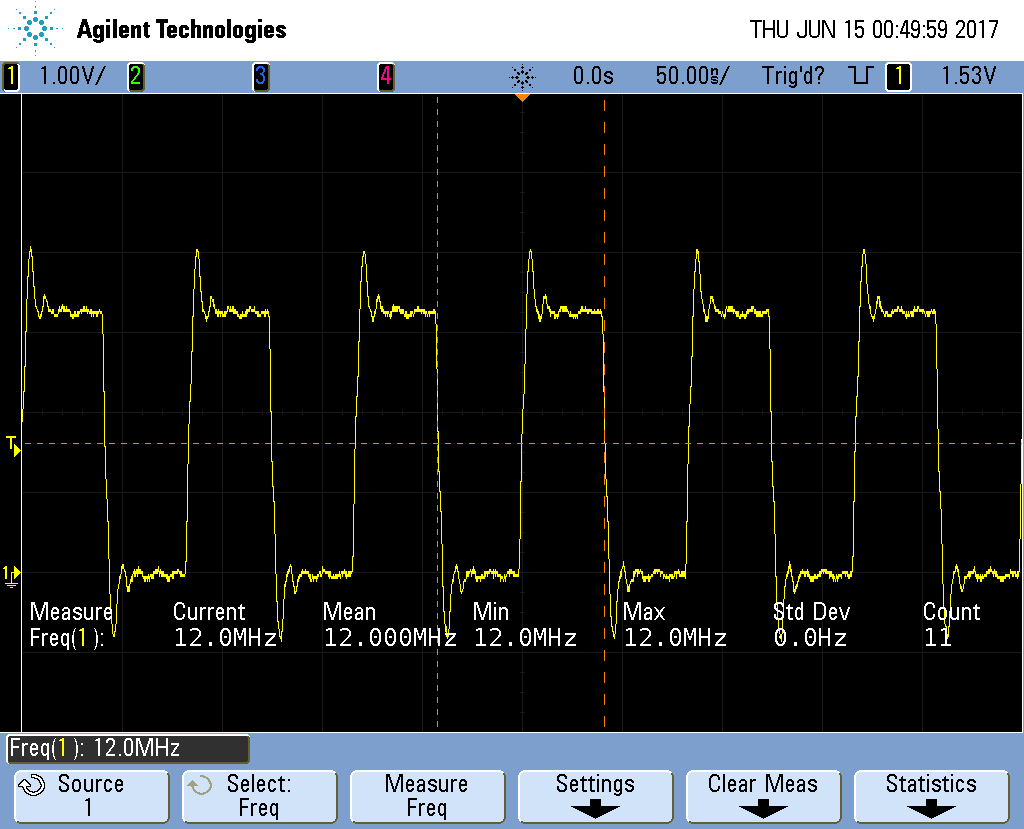

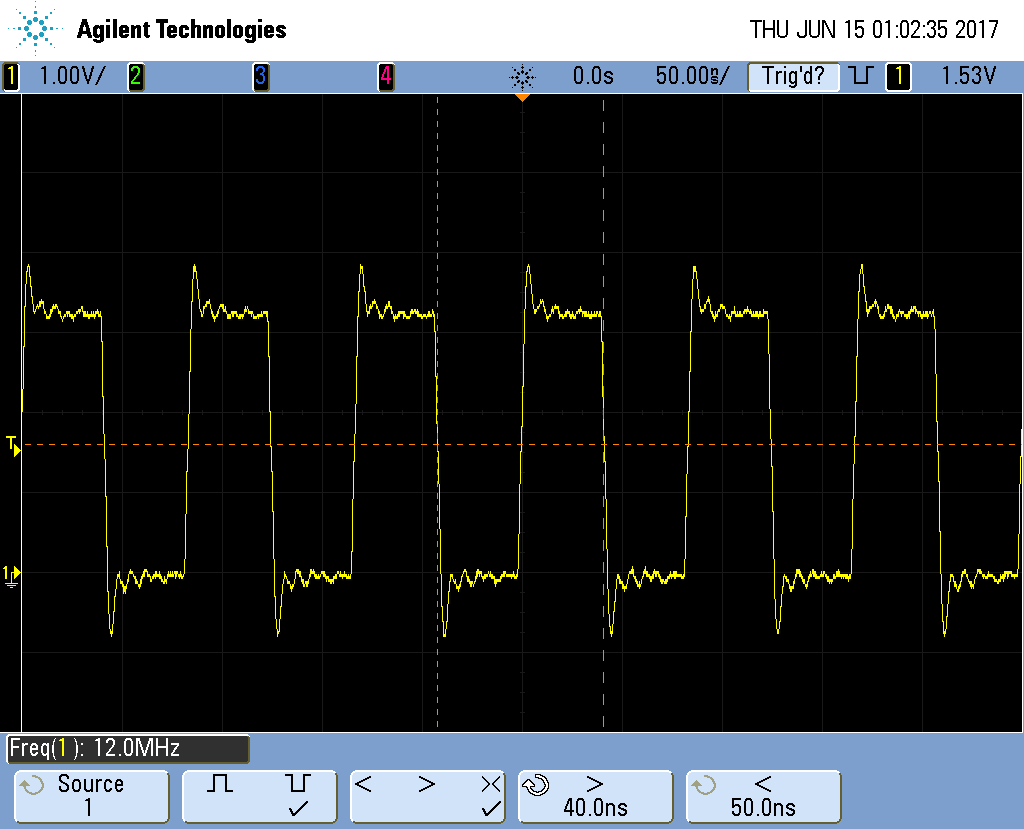

We are trying to boot into a linux operating system using the MMC0 interface. It appears that the processor starts and does the intitial interaction with the MMC0 port, it seems that it does communicate with the SD card. The processor then goes to a higher speed clock (25MHz) and it will still communicate to the SD card using the CMD line, data looks to be sent on the D0 line but it will not go beyond this.

I am not sure what else to look at for debugging this issue, we have double checked and verified the bootstrapping pins and they are correct. Any help would be greatly appreciated.