Hello,

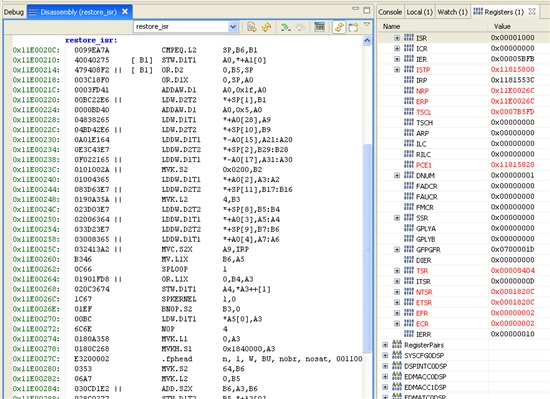

When I start a debug session with CCS4 the FIRST TIME after powering up the OMAPL138 Experimenter Kit, the C674x always gets an exception. The EXC_dispatcher in turn redirects processing to UTL_halt(). When I terminate the first debug session in CCS4 and start it again (without power cycling the board) everything works fine. As you can see in EFR an internal exception occurred. As you can see in IERR it was a ressource conflict. The code which caused the ressource conflict is shown on the left side of the screen dump. It is code of the BIOS int dispatcher.

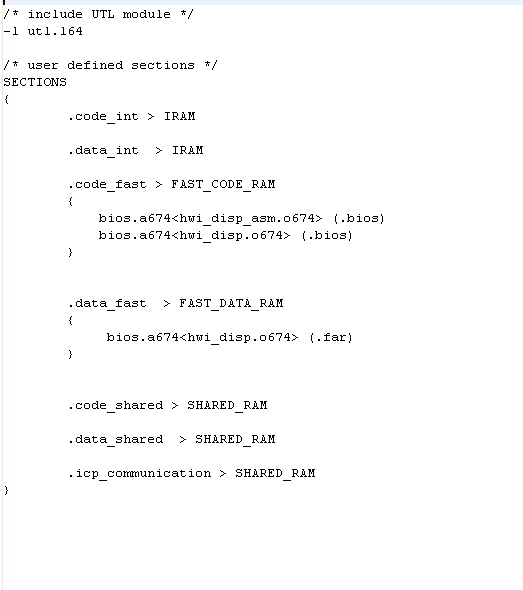

The exception only occurs when I map the int dispatcher data and code into L1 RAM. The corresponding Linker command file is shown below. When I remove the lines which map the int dispatcher data and code to L1 RAM, there is no exception upon the first run after power up.

What does ressource conflict mean? Why does it only occur when I map the int dispatcher to L1 RAM? Why does it only occurr the first time after powering up the board?

Thanks in advance