Chapter 8.4 in http://www.ti.com/lit/ds/sprs957d/sprs957d.pdf about PDN implementation guidance states that "TI supports only designs that follow the board design guidelines contained in the http://www.ti.com/lit/pdf/spraby8 application report.

This report deals with the AM572x MPUs and not the AM571x MPUs. Not a big problem, but what's more of a problem is the recommendations about the decoupling capacitors in table 2.

| Supply | 100 nF | 220 nF | 470 nF | 1 uF | 2.2 uF | 4.7 uF | 22 uF |

| vdd_mpu | 12 | 2 | 2 | 3 | 1 | 1 | 1 |

These recommendations are not perfectly in line with the recommendations at http://processors.wiki.ti.com/index.php/General_hardware_design/BGA_PCB_design/BGA_decoupling that states that:

"Based on the fact that often differing values of capacitors cause more harm than good (because of the resonance possibility listed above), and the fact that with newer capacitor dielectrics, larger value capacitors have the nearly identical high frequency impedance as their smaller value counterparts in the same body size, we recommend using just one value, 0.1uF-0.2uF, in the smallest package manufacturable by your company (this should be 0402 size or smaller). "

Or are the > 100 nF capacitors to be considered as bulk capacitors?

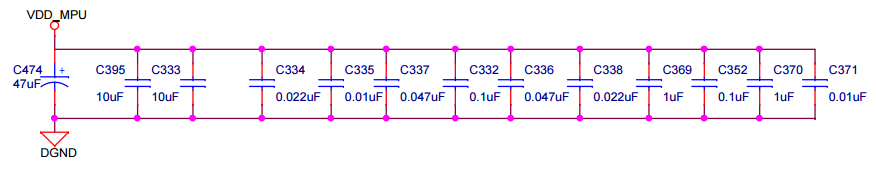

In any case, it's interesting to note that the AM5718 reference design (http://www.ti.com/lit/df/sprr242/sprr242.pdf) definitely doesn't follow the above recommendations.

Different schools within TI?

Best Regards

/F