Tool/software: TI-RTOS

Hi,

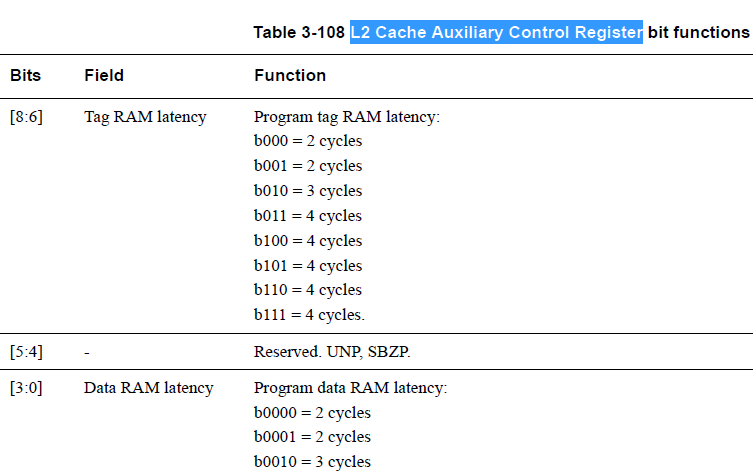

We would like to know what value should we use for Tag RAM latency/Data RAM latency

bits when enabling the L2 Cache (Cortex-A8 L2 Cache Auxiliary Control Register).

Couldn't find details on the ARM TRM or AM335x manuals.

Should these bits be left at default value?