Hi,

I have a am4376 based custom board with dp83849ivs [instead of KSZ9031RN in EVM].

I made below changes in code but still unable to send or receive data through eth0.

Could you please check the below changes and guide us to resolve the issue.

Disabled the MAC in u-boot Device tree:

-&mac {

+/* &mac {

slaves = <1>;

pinctrl-names = "default", "sleep";

pinctrl-0 = <&cpsw_default>;

pinctrl-1 = <&cpsw_sleep>;

status = "okay";

-};

+}; */

Added the mux entries in u-boot mux.c

+

+static struct module_pin_mux mii1_pin_mux[] = {

+ {OFFSET(mii1_txen), MODE(0)},

+ {OFFSET(mii1_rxdv), MODE(0) | RXACTIVE},

+ {OFFSET(mii1_txd3), MODE(0)},

+ {OFFSET(mii1_txd2), MODE(0)},

+ {OFFSET(mii1_txd1), MODE(0)},

+ {OFFSET(mii1_txd0), MODE(0)},

+ {OFFSET(mii1_txclk), MODE(0)},

+ {OFFSET(mii1_rxclk), MODE(0) | RXACTIVE},

+ {OFFSET(mii1_rxd3), MODE(0) | RXACTIVE},

+ {OFFSET(mii1_rxd2), MODE(0) | RXACTIVE},

+ {OFFSET(mii1_rxd1), MODE(0) | RXACTIVE},

+ {OFFSET(mii1_rxd0), MODE(0) | RXACTIVE},

+ {-1},

+};

+

+static struct module_pin_mux mii2_pin_mux[] = {

+ {OFFSET(gpmc_a0), MODE(1)},

+ {OFFSET(gpmc_a1), MODE(1) | RXACTIVE},

+ {OFFSET(gpmc_a2), MODE(1)},

+ {OFFSET(gpmc_a3), MODE(1)},

+ {OFFSET(gpmc_a4), MODE(1)},

+ {OFFSET(gpmc_a5), MODE(1)},

+ {OFFSET(gpmc_a6), MODE(1)},

+ {OFFSET(gpmc_a7), MODE(1) | RXACTIVE},

+ {OFFSET(gpmc_a8), MODE(1) | RXACTIVE},

+ {OFFSET(gpmc_a9), MODE(1) | RXACTIVE},

+ {OFFSET(gpmc_a10), MODE(1) | RXACTIVE},

+ {OFFSET(gpmc_a11), MODE(1) | RXACTIVE},

+ {-1},

+};

@@ -134,6 +167,8 @@ void enable_board_pin_mux(void)

configure_module_pin_mux(mmc0_pin_mux);

configure_module_pin_mux(i2c0_pin_mux);

configure_module_pin_mux(mdio_pin_mux);

+ configure_module_pin_mux(mii1_pin_mux);

+ configure_module_pin_mux(mii2_pin_mux);

Below changes in Linux device tree:

=============================

diff --git a/arch/arm/boot/dts/am437x-gp-evm.dts b/arch/arm/boot/dts/am437x-gp-evm.dts

index 49ab9520f16..083ede3d3e0 100644

--- a/arch/arm/boot/dts/am437x-gp-evm.dts

+++ b/arch/arm/boot/dts/am437x-gp-evm.dts

@@ -246,44 +246,50 @@

>;

};

+ cpsw_default: cpsw_default {

+ pinctrl-single,pins = <

+

+ /* Slave 1*/

+ /* 0x108 ( PIN_INPUT_PULLDOWN | MUX_MODE0 ) */ /* (D16) mii1_col.gmii1_col */

+ /* 0x10c ( PIN_INPUT_PULLDOWN | MUX_MODE0 ) */ /* (B14) mii1_crs.gmii1_crs */

+

+ 0x110 ( PIN_INPUT_PULLDOWN | MUX_MODE0 ) /* (B13) mii1_rx_er.gmii1_rxer */

+ 0x114 ( PIN_OUTPUT_PULLDOWN| MUX_MODE0) /* (A13) mii1_tx_en.gmii1_txen */

+ 0x118 ( PIN_INPUT_PULLDOWN | MUX_MODE0 ) /* (A15) mii1_rx_dv.gmii1_rxdv */

+ 0x12c ( PIN_INPUT_PULLDOWN | MUX_MODE0 ) /* (D14) mii1_tx_clk.gmii1_txclk */

+ 0x130 ( PIN_INPUT_PULLDOWN | MUX_MODE0 ) /* (D13) mii1_rx_clk.gmii1_rxclk */

+ 0x128 ( PIN_OUTPUT_PULLDOWN | MUX_MODE0) /* (B15) mii1_txd0.gmii1_txd0 */

+ 0x124 ( PIN_OUTPUT_PULLDOWN | MUX_MODE0) /* (A14) mii1_txd1.gmii1_txd1 */

+ 0x120 ( PIN_OUTPUT_PULLDOWN | MUX_MODE0) /* (C13) mii1_txd2.gmii1_txd2 */

+ 0x11c ( PIN_OUTPUT_PULLDOWN | MUX_MODE0) /* (C16) mii1_txd3.gmii1_txd3 */

+ 0x140 ( PIN_INPUT_PULLDOWN | MUX_MODE0 ) /* (F17) mii1_rxd0.gmii1_rxd0 */

+ 0x13c ( PIN_INPUT_PULLDOWN | MUX_MODE0 ) /* (B16) mii1_rxd1.gmii1_rxd1 */

+ 0x138 ( PIN_INPUT_PULLDOWN | MUX_MODE0 ) /* (E16) mii1_rxd2.gmii1_rxd2 */

+ 0x134 ( PIN_INPUT_PULLDOWN | MUX_MODE0 ) /* (C14) mii1 */

+

+

+ /* Slave 2 */

+ /* 0x78 ( PIN_INPUT_PULLUP | MUX_MODE1 ) */ /* (A3) gpmc_be1n.gmii2_col */

+ /* 0x84 ( PIN_INPUT_PULLUP | MUX_MODE8 ) */ /* (F10) gpmc_csn2.gmii2_crs */

+

+ 0x74 ( PIN_INPUT_PULLUP | MUX_MODE1 ) /* (B3) gpmc_wpn.gmii2_rxer */

+ 0x40 ( PIN_OUTPUT_PULLDOWN | MUX_MODE1) /* (C3) gpmc_a0.gmii2_txen */

+ 0x44 ( PIN_INPUT_PULLDOWN | MUX_MODE1 ) /* (C5) gpmc_a1.gmii2_rxdv */

+ 0x58 ( PIN_INPUT_PULLDOWN | MUX_MODE1 ) /* (E8) gpmc_a6.gmii2_txclk */

+ 0x5c ( PIN_INPUT_PULLDOWN | MUX_MODE1 ) /* (F6) gpmc_a7.gmii2_rxclk */

+ 0x54 ( PIN_OUTPUT_PULLDOWN | MUX_MODE1) /* (E7) gpmc_a5.gmii2_txd0 */

+ 0x50 ( PIN_OUTPUT_PULLDOWN | MUX_MODE1) /* (D7) gpmc_a4.gmii2_txd1 */

+ 0x4c ( PIN_OUTPUT_PULLDOWN | MUX_MODE1) /* (A4) gpmc_a3.gmii2_txd2 */

+ 0x48 ( PIN_OUTPUT_PULLDOWN | MUX_MODE1) /* (C6) gpmc_a2.gmii2_txd3 */

+ 0x6c ( PIN_INPUT_PULLDOWN | MUX_MODE1 ) /* (D8) gpmc_a11.gmii2_rxd0 */

+ 0x68 ( PIN_INPUT_PULLDOWN | MUX_MODE1 ) /* (G8) gpmc_a10.gmii2_rxd1 */

+ 0x64 ( PIN_INPUT_PULLDOWN | MUX_MODE1 ) /* (B4) gpmc_a9.gmii2_rxd2 */

+ 0x60 ( PIN_INPUT_PULLDOWN | MUX_MODE1 ) /* (F7) gpmc_a8.gmii2_rxd3 */

- cpsw_default: cpsw_default {

- pinctrl-single,pins = <

- /* Slave 1 */

- 0x114 (PIN_OUTPUT_PULLDOWN | MUX_MODE2) /* mii1_txen.rgmii1_txen */

- 0x118 (PIN_INPUT_PULLDOWN | MUX_MODE2) /* mii1_rxdv.rgmii1_rxctl */

- 0x11c (PIN_OUTPUT_PULLDOWN | MUX_MODE2) /* mii1_txd1.rgmii1_txd3 */

- 0x120 (PIN_OUTPUT_PULLDOWN | MUX_MODE2) /* mii1_txd0.rgmii1_txd2 */

- 0x124 (PIN_OUTPUT_PULLDOWN | MUX_MODE2) /* mii1_txd1.rgmii1_txd1 */

- 0x128 (PIN_OUTPUT_PULLDOWN | MUX_MODE2) /* mii1_txd0.rgmii1_txd0 */

- 0x12c (PIN_OUTPUT_PULLDOWN | MUX_MODE2) /* mii1_txclk.rmii1_tclk */

- 0x130 (PIN_INPUT_PULLDOWN | MUX_MODE2) /* mii1_rxclk.rmii1_rclk */

- 0x134 (PIN_INPUT_PULLDOWN | MUX_MODE2) /* mii1_rxd1.rgmii1_rxd3 */

- 0x138 (PIN_INPUT_PULLDOWN | MUX_MODE2) /* mii1_rxd0.rgmii1_rxd2 */

- 0x13c (PIN_INPUT_PULLDOWN | MUX_MODE2) /* mii1_rxd1.rgmii1_rxd1 */

- 0x140 (PIN_INPUT_PULLDOWN | MUX_MODE2) /* mii1_rxd0.rgmii1_rxd0 */

- >;

- };

+ >;

+ };

- cpsw_sleep: cpsw_sleep {

- pinctrl-single,pins = <

- /* Slave 1 reset value */

- 0x114 (PIN_INPUT_PULLDOWN | MUX_MODE7)

- 0x118 (PIN_INPUT_PULLDOWN | MUX_MODE7)

- 0x11c (PIN_INPUT_PULLDOWN | MUX_MODE7)

- 0x120 (PIN_INPUT_PULLDOWN | MUX_MODE7)

- 0x124 (PIN_INPUT_PULLDOWN | MUX_MODE7)

- 0x128 (PIN_INPUT_PULLDOWN | MUX_MODE7)

- 0x12c (PIN_INPUT_PULLDOWN | MUX_MODE7)

- 0x130 (PIN_INPUT_PULLDOWN | MUX_MODE7)

- 0x134 (PIN_INPUT | PULL_DISABLE | MUX_MODE7)

- 0x138 (PIN_INPUT | PULL_DISABLE | MUX_MODE7)

- 0x13c (PIN_INPUT | PULL_DISABLE | MUX_MODE7)

- 0x140 (PIN_INPUT | PULL_DISABLE | MUX_MODE7)

-

- >;

- };

davinci_mdio_default: davinci_mdio_default {

pinctrl-single,pins = <

@@ -1034,9 +1040,10 @@

&mac {

slaves = <1>;

- pinctrl-names = "default", "sleep";

+ /* pinctrl-names = "default", "sleep"; */

+ pinctrl-names = "default";

pinctrl-0 = <&cpsw_default>;

- pinctrl-1 = <&cpsw_sleep>;

+/* pinctrl-1 = <&cpsw_sleep>; */

status = "okay";

};

@@ -1048,8 +1055,8 @@

};

&cpsw_emac0 {

- phy_id = <&davinci_mdio>, <0>;

- phy-mode = "rgmii";

+ phy_id = <&davinci_mdio>, <3>;

+ phy-mode = "mii";

};

minicom log :

eth0 Link encap:Ethernet HWaddr C4:BE:84:CB:12:32

inet6 addr: fe80::c6be:84ff:fecb:1232%132688/64 Scope:Link

UP BROADCAST RUNNING MULTICAST MTU:1500 Metric:1

RX packets:0 errors:0 dropped:0 overruns:0 frame:0

TX packets:43 errors:0 dropped:0 overruns:0 carrier:0

collisions:0 txqueuelen:1000

RX bytes:0 (0.0 B) TX bytes:7637 (7.4 KiB)

Interrupt:143

lo Link encap:Local Loopback

inet addr:127.0.0.1 Mask:255.0.0.0

inet6 addr: ::1%132688/128 Scope:Host

UP LOOPBACK RUNNING MTU:65536 Metric:1

RX packets:323 errors:0 dropped:0 overruns:0 frame:0

TX packets:323 errors:0 dropped:0 overruns:0 carrier:0

collisions:0 txqueuelen:1

RX bytes:24632 (24.0 KiB) TX bytes:24632 (24.0 KiB)

root@am437x-evm:~# ethtool eth0

Settings for eth0:

Supported ports: [ TP MII ]

Supported link modes: 10baseT/Half 10baseT/Full

100baseT/Half 100baseT/Full

Supported pause frame use: No

Supports auto-negotiation: Yes

Advertised link modes: 10baseT/Half 10baseT/Full

100baseT/Half 100baseT/Full

Advertised pause frame use: No

Advertised auto-negotiation: Yes

Link partner advertised link modes: 10baseT/Half 10baseT/Full

100baseT/Half 100baseT/Full

Link partner advertised pause frame use: Symmetric Receive-only

Link partner advertised auto-negotiation: Yes

Speed: 100Mb/s

Duplex: Full

Port: MII

PHYAD: 3

Transceiver: external

Auto-negotiation: on

Supports Wake-on: d

Wake-on: d

Current message level: 0x00000000 (0)

Link detected: yes

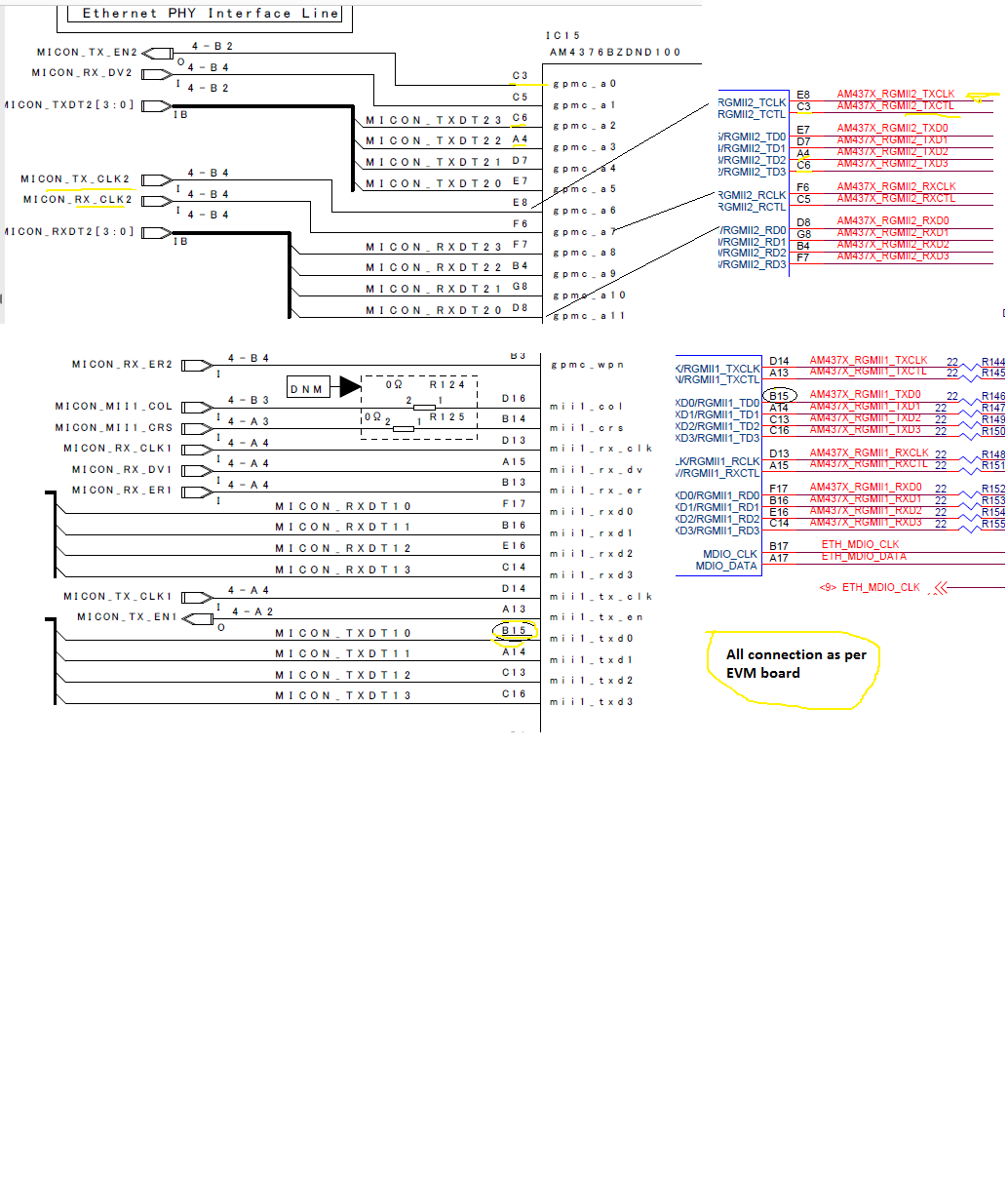

I attached pin compare diagram

Thanks in advance