Tool/software: Linux

Hello Gurus,

Im working on a custom board based on AM4377.

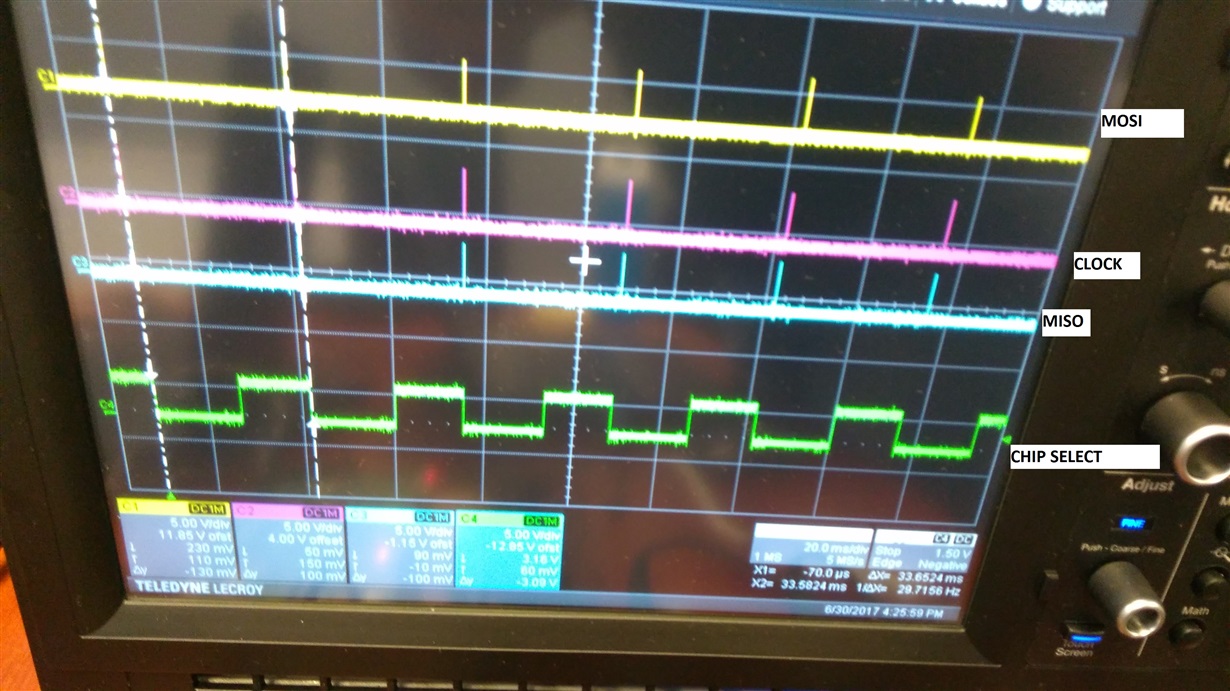

Im facing an issue related to SPI chip select timing where in the chip select stays low and high for a longer duration.

I would like to have the chip select go high post transmitting and receiving 32 bits of data(32 clock ticks) to and from the FPGA slave device.(Apart from t-lead and t-lag delays.)

The SPI enable(assertion) is automated.

I tried working on various time control of chip select toggle(TCS0) without any luck and the duration remains the same.

Chip Select Time Control This

2-bits field defines the number of interface clock cycles between CS

toggling and first or last edge of SPI clock.

0h (R/W) = 0.5 clock cycle

1h (R/W) = 1.5 clock cycle

2h (R/W) = 2.5 clock cycle

3h (R/W) = 3.5 clock cycle

The chip select duration remains the same for 0.5, 1.5, 2.5 and 3.5 clock cycles.

Following picture below gives you a better idea of the chip select behavior with respect to clock, MISO and MOSI.

So, could you please help me with a better timing control of the chip select?

Thanks in advance.

Best Regards

Rohit.