Part Number: TDA3

Hi,

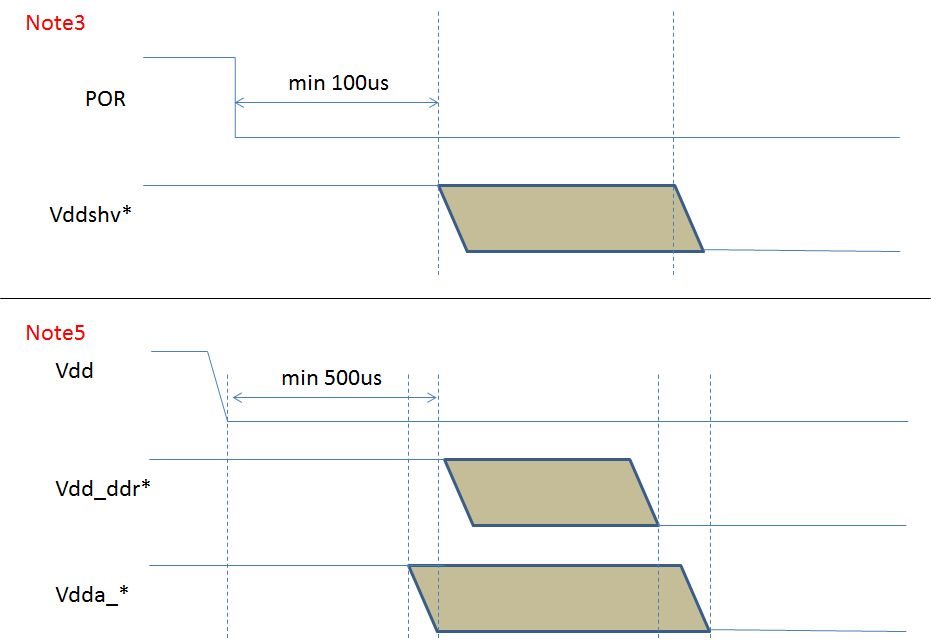

I have questions about power down sequence, Figure 5-2. Power-Down Sequencing on TDA3x DM.

1) Note4 is written as follows:

(4) vdd_dspeve can ramp down before or at the same time as vdd/vpp.

What dose Vpp mean?

2) About Note7:

(7) xi_osc0 can be turned off anytime after porz assertion and must be turned off before vdda_osc voltage rail is shutdown.

Who is tun off or control xi_osc0? xi_osc0 connects crystal. so, I can't control it.

Regards,

Kenshow