Tool/software: TI-RTOS

Hi,

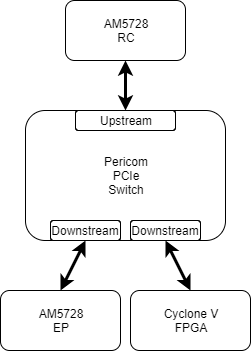

In our custom board, we have 3 ports Pericom switch on which we connected 2 Sitara processors and 1 Cyclone V FPGA:

So far, we managed to get PCIe link-up on both the AM5728. Now, I would like to perform the PCIe enumeration on the RC. Both the EP and RC code is running within the C66 DSP core. I understand the PCIe enumeration as stated in the following thread:

I have previously implemented such procedure on the KeyStone-II device. In KeyStone-II I used the 'Configuration Transaction Setup Register' (CFG_SETUP) register to perform that operation.

However, that register is not supported on the Sitara processor. I have read section 24.9.4.8.2.2 of the AM5728 TRM (multiple times) and don't understand exactly how this can be accomplish with the Pciev1_atuRegionConfig function.

Any help will be greatly appreciated.

- David