Part Number: DRA750

Tool/software: Linux

Hi expert,

1. I use GLSDK 3.02.00.03, sometimes error occur when dwc3 register ULPI interface.

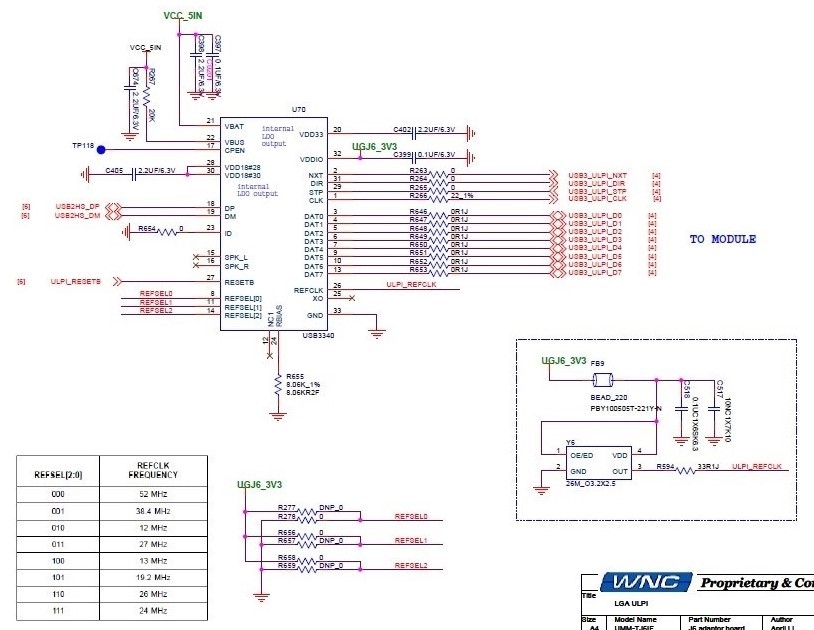

2. I use Microchip USB3340 as ULPI PHY and its reference clock set to 26 MHz (OUTPUT Mode, REFSEL[2:0] 110), it can let ULPI PHY to generate 60 MHz clock to CPU module.

3. Error message shows:

[ 5.597565] dwc3 48910000.usb: failed to register ULPI interface

4. I found the function ulpi_write(ulpi, ULPI_SCRATCH, 0xaa) in ulpi_register() error, that is, return value is -110 by dwc3_ulpi_busyloop(dwc) in dwc3_ulpi_write(), count=1000 and decrease to 0 and then timeout value ETIMEDOUT returned.

Could you please help to provide debug procedure.

Thank you.

BRs

Louis