Part Number: TDA3

Hello.

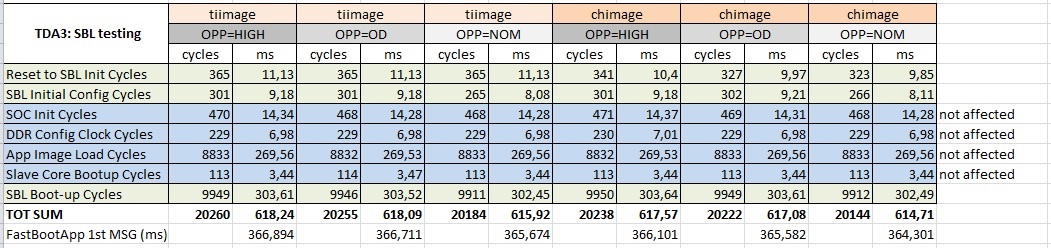

I'm trying to compare 'sbl.chimage' over 'sbl.tiimage'.

I can't see any speed advantage for the chimage-version while booting from qspi-flash (TDA3XXEVM).

The chimage-header is correct?

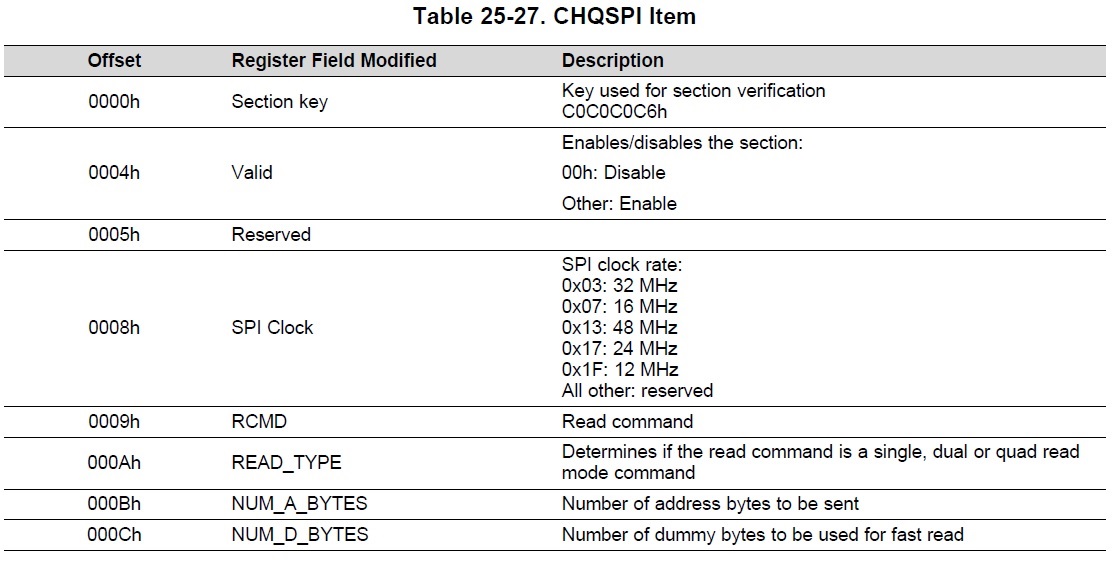

Here is Table 25-27 from TRM.

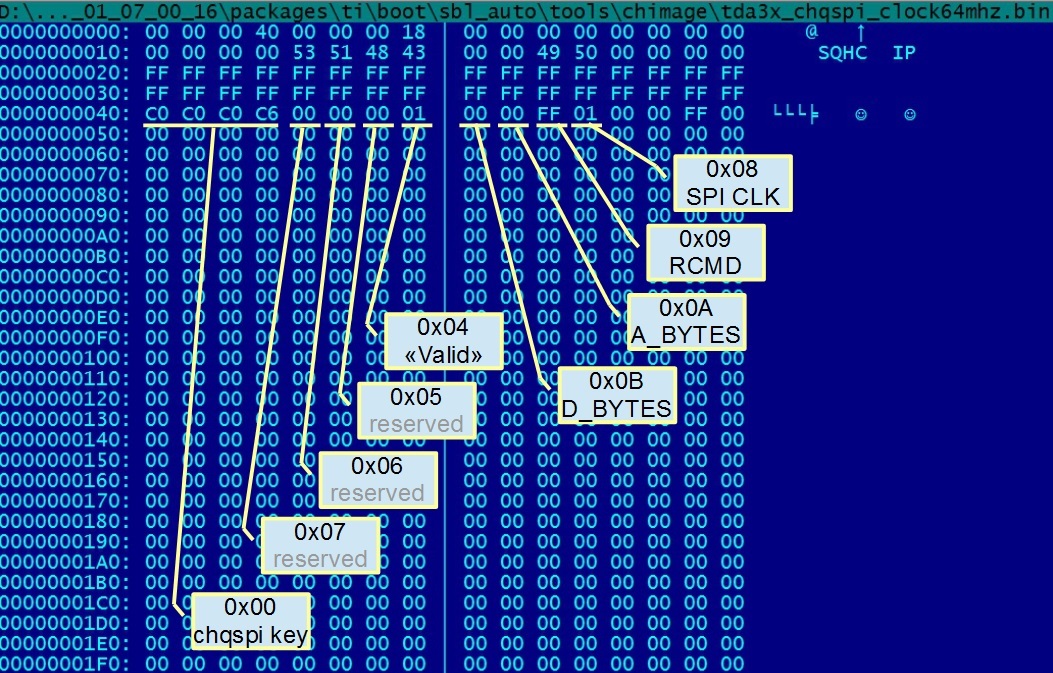

But, here is content of

'ti_components/drivers/pdk_01_07_00_16/packages/ti/boot/sbl_auto/tools/chimage/tda3x_chqspi_clock64mhz.bin'

Here is result:

0x040 (0x00) Section key : "C0 C0 C0 C6" = OK

0x044 (0x04) Valid : "00" = (disable) ???

0x045 (0x05) Reserved : "00"

0x046-0x047 : "00 01" = (unknown fields) !!

0x048 (0x08) SPI Clock : "00" = (All other: Reserved) ???

0x049 (0x09) RCMD : "00" = ?

0x04A (0x0A) READ_TYPE : "FF" = ?

0x04B (0x0B) NUM_A_BYTES : "01" = ?

0x04C (0x0C) NUM_D_BYTES : "00" = ?

0x04D-0x04F : "00 FF 00" = (unknown fields) !!

Why 'valid' is disabled? Where are 64Mhz speed selection? Could you explain RCMD,READ_TYPE,NUM_A_BYTES and NUM_D_BYTES fields? Does the file name (offs:0x014-0x01F) have any meaning?

Thank you in advance.

PS: Vision SDK is 3.0.0.0