Hi all,

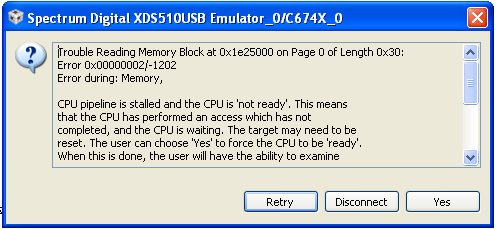

I have a customer that is having problems to connect to CCS in his custom board (but not in the EVM), he is getting this error (clicking "yes" did not solve it):

We analyzed the problem and it does not seem to be a CCS issue as he did not make any updates and the same software and same GEL file work fine in the EVM.

When the problem started occurring, no hardware changes were made. The problem occurred the first time he tried to access the USB1 peripheral module. No initialization changes were made. Error occurs even before any software is sent to the board. No upgrades in CCS have been made in a while.

Both devices are: XOMAPL137ZKB3 or:Experimental OmapL137 SiliconRev1.0 0-90*C 256BGA 300MHZ

I asked to make sure that the board was in EMU boot and he did, but no change.

Could it be related to some USB state? Is there more information on SPRZ291D: Advisory 1.1.9 (Slew rate on USB0 and USB1 power supplies)?