Part Number: AM4372

Other Parts Discussed in Thread: TPS65218

Hi champs,

My customer has a question about AM437x power down sequence time requirement.

I saw Sitara datasheet 5.13.1.3 Power-Down Sequencing.

It does not write the request for Time.

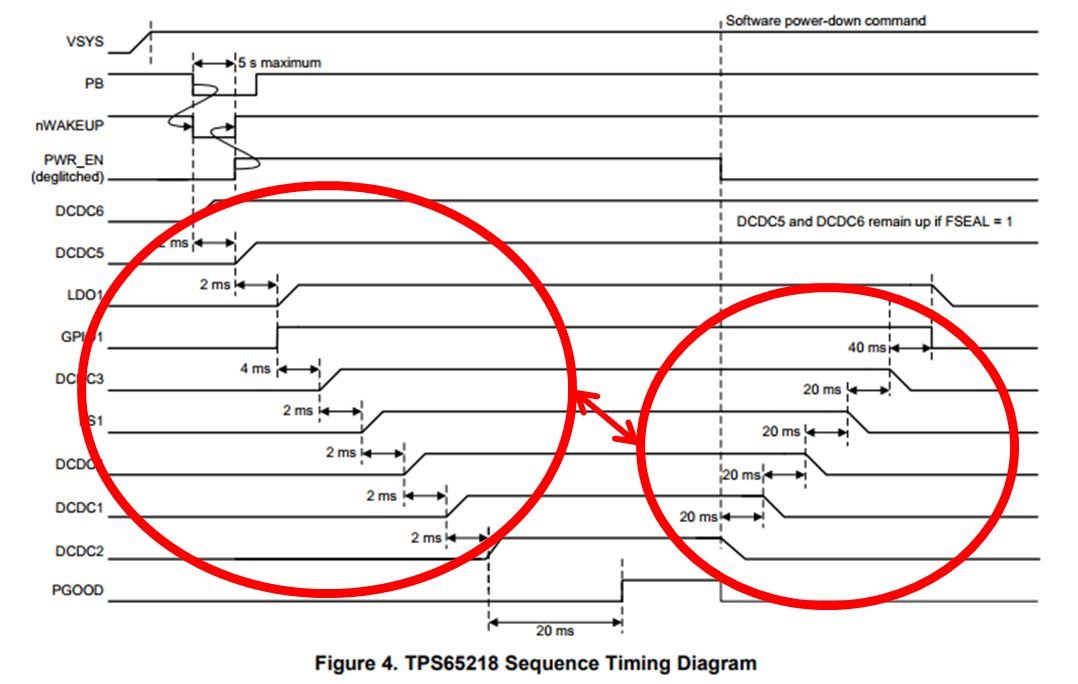

Other document, "Powering the AM335x, AM437x, and AM438x With TPS65218"

P.8 8 Power-Up and Power-Down Sequence for TPS65218.

Sequence power down time is bigger than power up time.

Question

Do we have to keep the power down time written in this figure?

If it is the same time as power up time(like a 2ms~4ms), we can reduce the big capacitor.

Please let me know.

Regards,

Shinji Ueda