Part Number: TMS320C6678

Tool/software: TI-RTOS

Hello,

We've designed a system similar to C6678 EVM where the C6678 DSP is connected to Virtex 7 FPGA via the PCIe Gen2 x2. The DSP planned to be the Root Complex side.

The needed steps to do to verify the PCIe connection are reading:

- Vendor/Sub-system Vendor ID

- Device/Sub-system Device ID

- Class code

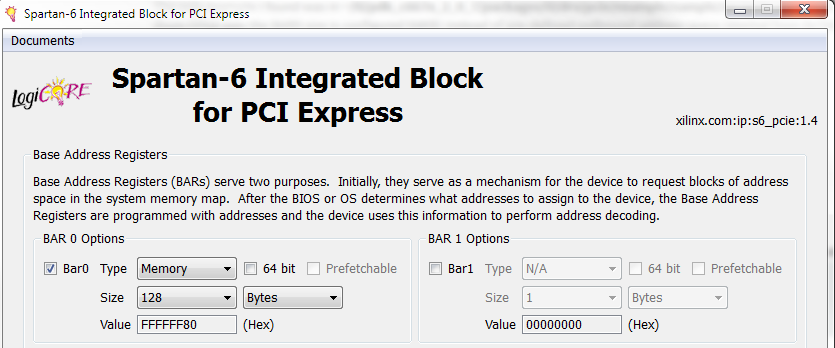

- Register offsets within Bar 0

The first 3 steps we've already succeeded to do but the 4th one is still the open side.

The only example I found was in ~/ti/pdk_c667x_2_0_7/packages/ti/drv/pcie/example/sample/src/pcie_sample.c path and I couldn't figure out how I can modify it to read the BAR0 space registers (from FPGA side the BAR0 size is configured 64KB) instead of pre-defined outbound address space (started from 0x70000000) and inbound address space (started from 0x90000000).

Could you please advice how to find the needed examples / modify the sources for it?

Regards

Andranik