Tool/software: Linux

We are using the DRA7xx infotainment processor J6 and the linux kernel 4.4.23.

In addition to the e2e post:

https://e2e.ti.com/support/arm/automotive_processors/f/1020/p/575710/2259260#2259260

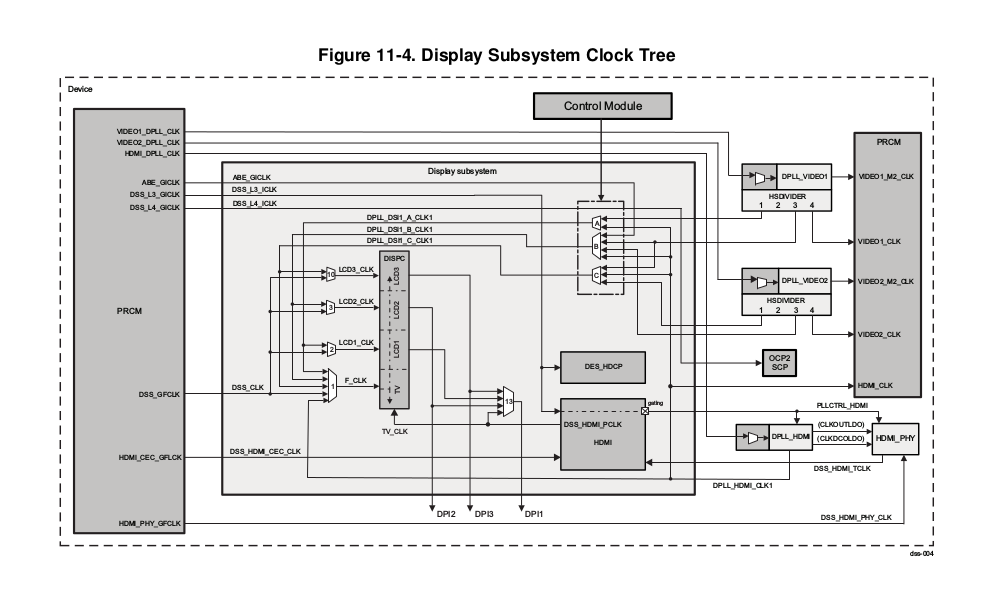

and with reference to the figure: Figure 11-4. Display Subsystem Clock Tree, see figure below.

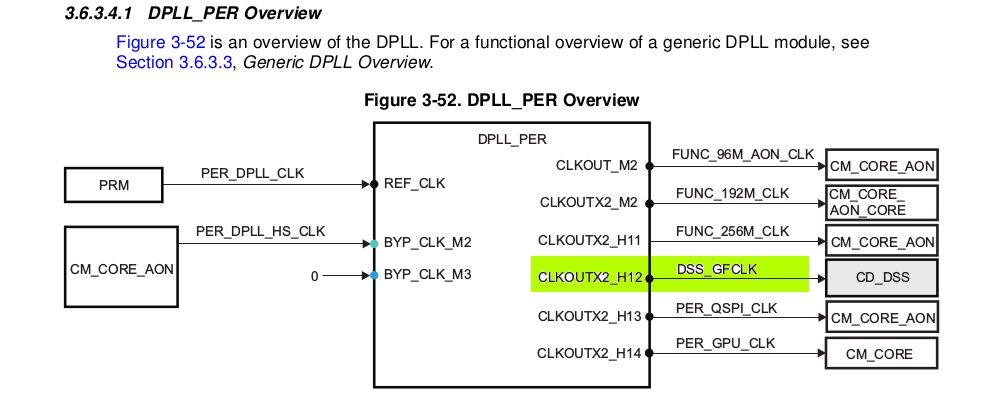

By default the hdmi driver (in the drivers/gpu/drm/omapdrm) is working with this configuration:

F_CLK (multiplexer 1) is sourced from DSS_CLK (DSS_CLK_SRC_FCK)

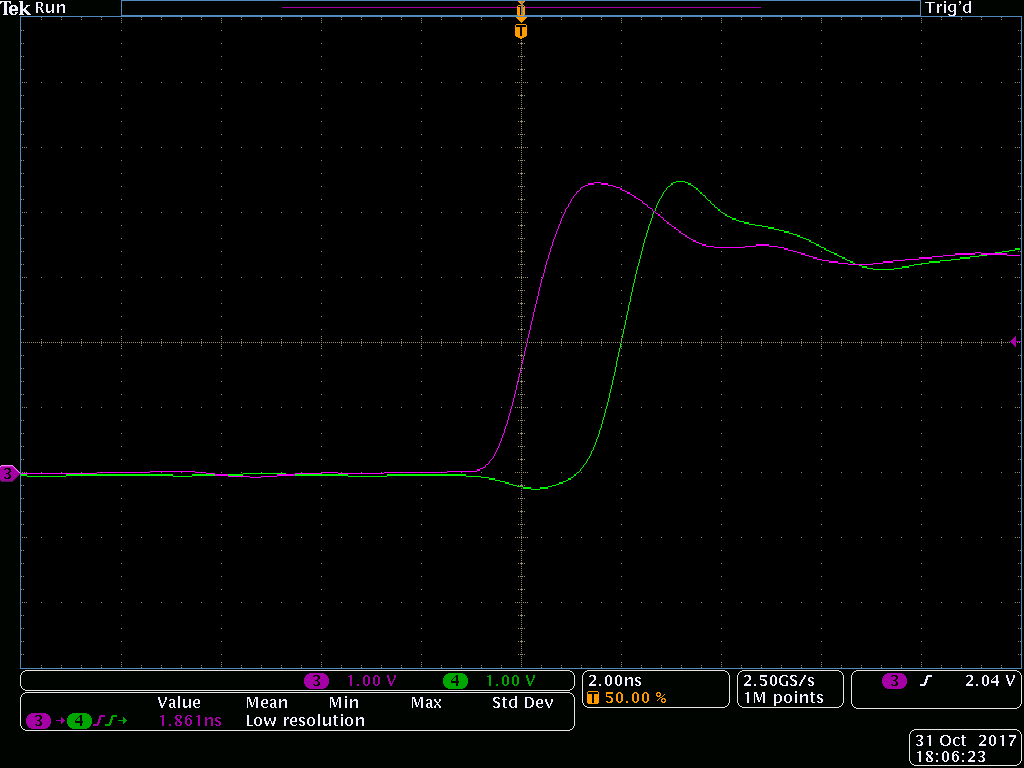

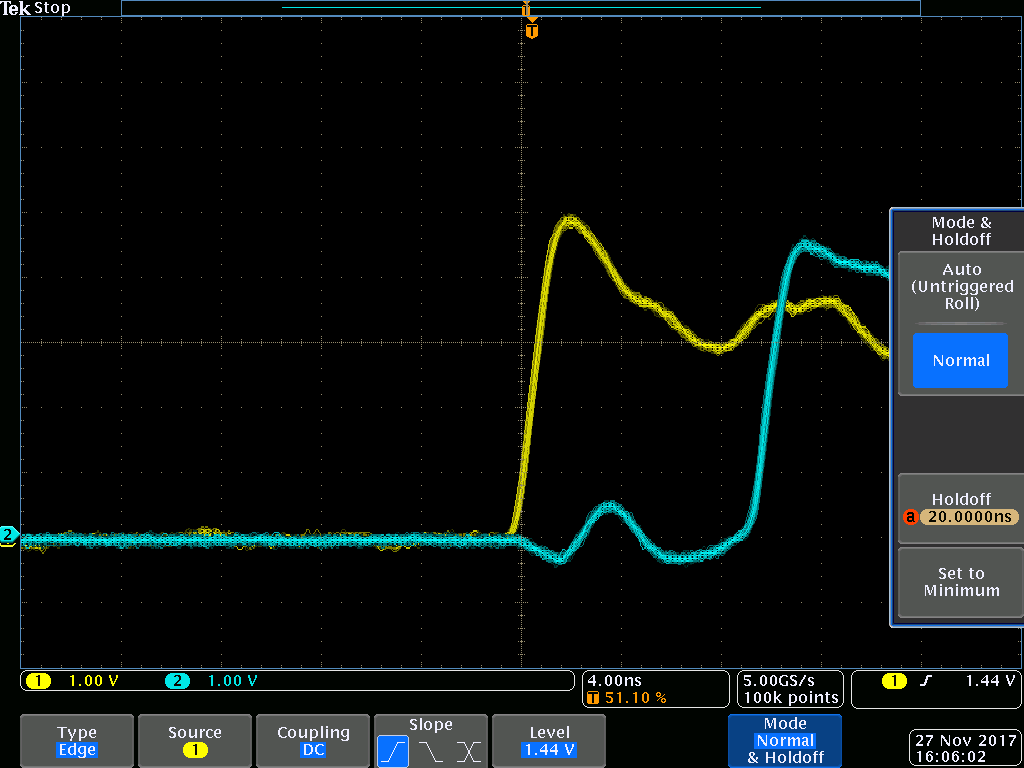

If we try to synchronize the LCDs using the common DSS_CLK source (instead of the Video PLL lines from DPLLs) and introducing a 'warmreset' before enabling the displays, the time between the 2 Vout HSYNC is ~2ns (see scope figure below).

But with this method the HDMI is no more working.

It is possible to configure the HDMI to use an internal generated clock instead of the default DSS_CLK?

How it is possible?