Part Number: AMIC110

Tool/software: TI-RTOS

Hi Team,

My customer now is using the AMIC110 for EtherCAT slave project. The software version is PROCESSOR SDK RTOS 03_03_00_04, PRU-ICSS-ETHERCAT-SLAVE 01_00_03_01.

For the hardware design, they chose to use the Micrel Semiconductor KSZ8041NLfollow the design of the design of the AMIC110 ICE EVM.

They're trying to use the EtherCAT full application demo, and it worked fine with the AMIC110 ICE. However, on their production board, after using the code on the production board, the link light was lighting but the EtherCAT cannot work.

when tracing the PHY register, they found some register settings doesn't have the same values as those on the AMIC110 ICE.

So they'd like to know:

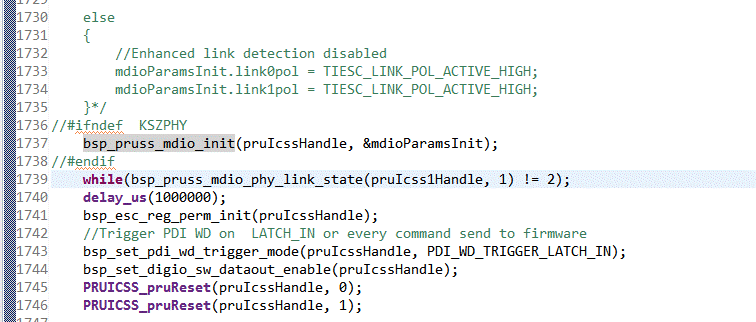

1. is there any document could help to understand the register values? I've attached an example.

2. is there any porting guide for this ethercat slave demo? for the Micrel Semiconductor KSZ8041NL

3. is there any debug guide for this issue debugging?