Tool/software: Linux

Hi,

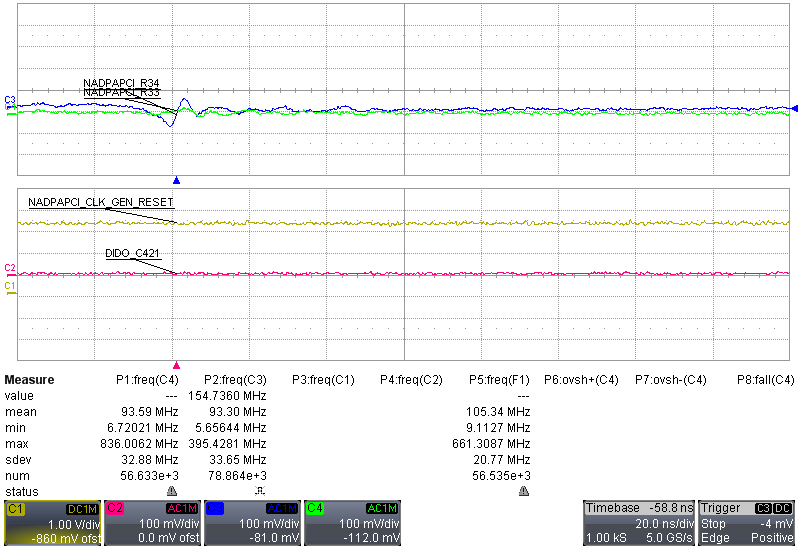

I have a question about a customer application based on a TMS320DM8148 processor, we've noticed an issue when trying to boot from cold temperature the kernel Linux with PCI enabled (CONFIG_PCI=Y).

Software hangs at

while (!(omap_ctrl_readl(TI814X_CONTROL_PCIE_PLLSTATUS) & 0x1))

cpu_relax();

in the file linux-omap3/arch/arm/mach-omap2/devices.c, waiting for PCIE PLL's lock.

The temperature which causes the issue can vary from each module, from ambient temperature down to 0°C (limit temperature for this P/N).

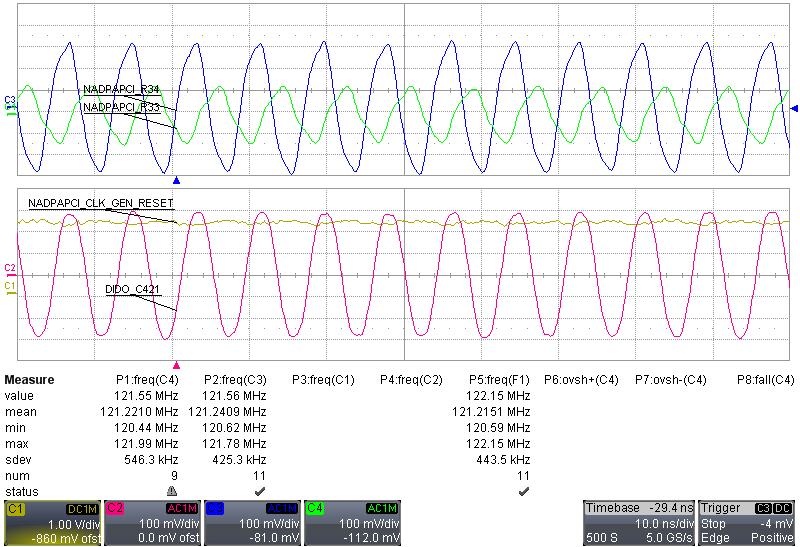

If we maintain the module powered, it warms up and boots after some minutes, if the reached temperature is hot enough.

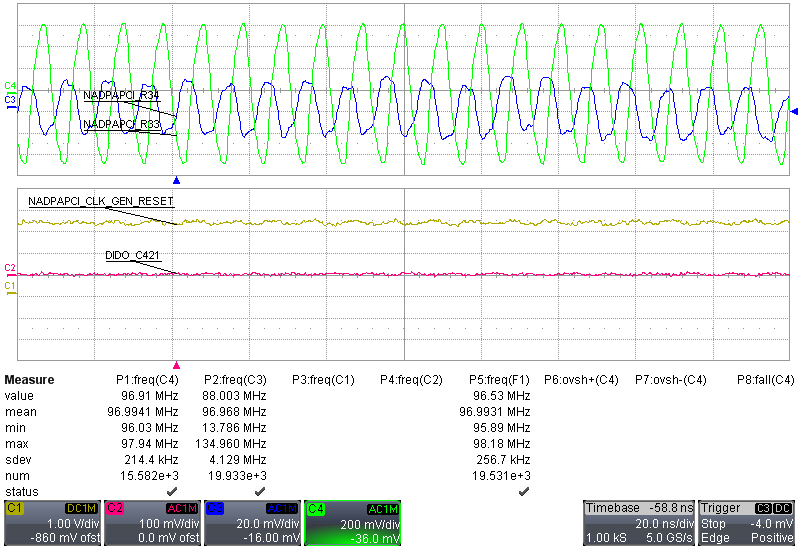

The module is clocked with a 20MHz crystal oscillator and the SERDES signals are clocked with a CDCM61002RHBx chip delivering a 100MHz source.

Can you help us to understand what can cause this issues?

Thanks

Umberto