Hi,

we have some problems booting the OMAPL138 from nor flash. We want to execute our test code directly out of the nor flash. The code is written to flash at address 0x60000004 (no ais image). When setting the pc to this address with the debugger, we can debug the code and everything works fine. But the on chip loader doesn't branch to this address. So we are not able to start our test code out of the flash when powering up our board.

Things to know:

BOOTCFG Register (address 0x1C14020): 0x00000002 -> NOR Boot

First word in flash (address 0x60000000): 0x......11 -> direct NOR boot, 16Bit flash access

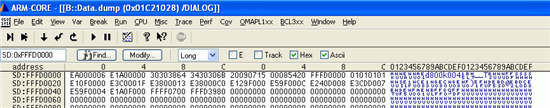

ARM ROM content (address 0xFFFD0000):

Any ideas???

Regards

Marc