Tool/software: Linux

Hi Expert:

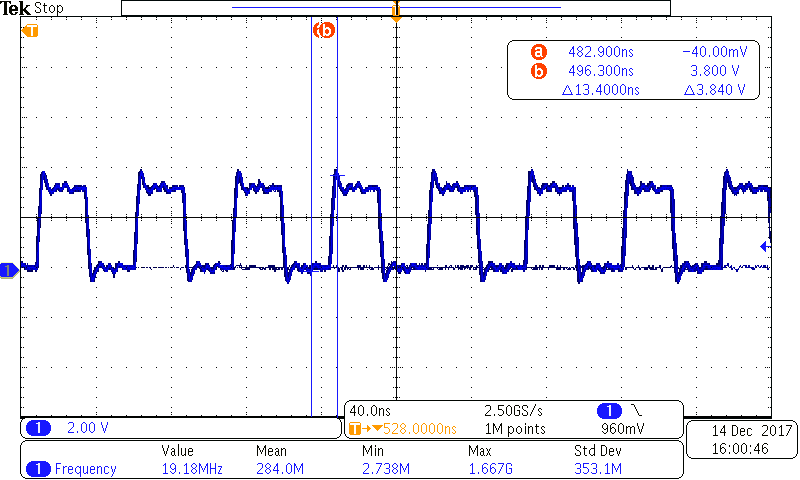

We find that visionsdk 2.12.02 the Linux operate QSPI speed setting at ~19Mhz.

At uboot we setting QSPI speed is 76.8MHz. (arch/arm/dts/dra71-evm.dts), probe the QSPI clock signal the speed is 76.8MHz.

But when kernel start, probe QSPI clock first it is 76.8MHz, when enter Linux console the QSPI read/write speed just 19MHz.

Default mode read 0x4b000040 it is 0x80000004.

use omapconf write 0x4b300040 0x80000001 change QSPI clock div from 4 to 1. the QSPI speed change to 76.8MHz at kernel.

Could you please help us check which part to code change the QSPI speed at kernel?

At DTS file we setting QSPI max speed is 76.8MHz, but we did not which part of code change the QSPI clock setting.

Best Regards!

Han Tao