Hi Sir

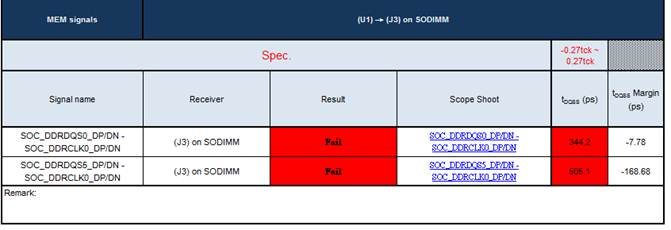

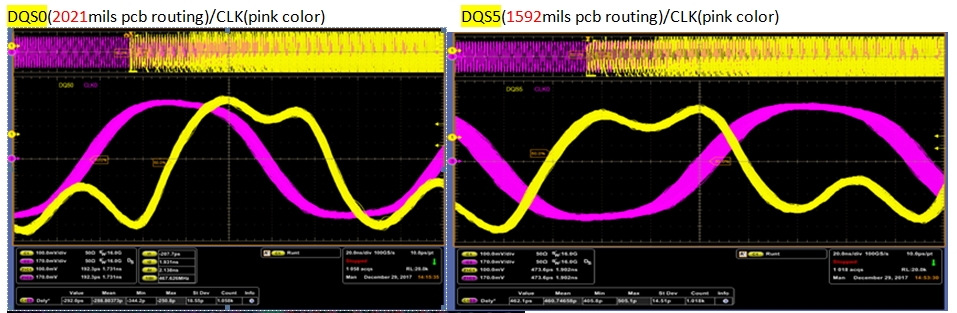

DQS/CLK skew failed probed on SO-DIMM connector as following picture for you reference.

There is no length matching rule for DQS/CLK in “keystone DDR3 length rules template” and EVM board.

Is any parameter setting in K2E can solve this issue or any solution to test this failed item?

BR

Yimin