one day, i started to load my .bin file to 6678 throgh net(before that day,using TFTP BOOT to load my .bin file was ok),for some reason i don't know,it can't be loaded.And i restart the power ,i find that the UART have no printf information,usually,it will have the information below:

IBL version: 1.0.0.16

IBL: PLL and DDR Initialization Complete

IBL Result code 00

IBL: Booting from ethernet

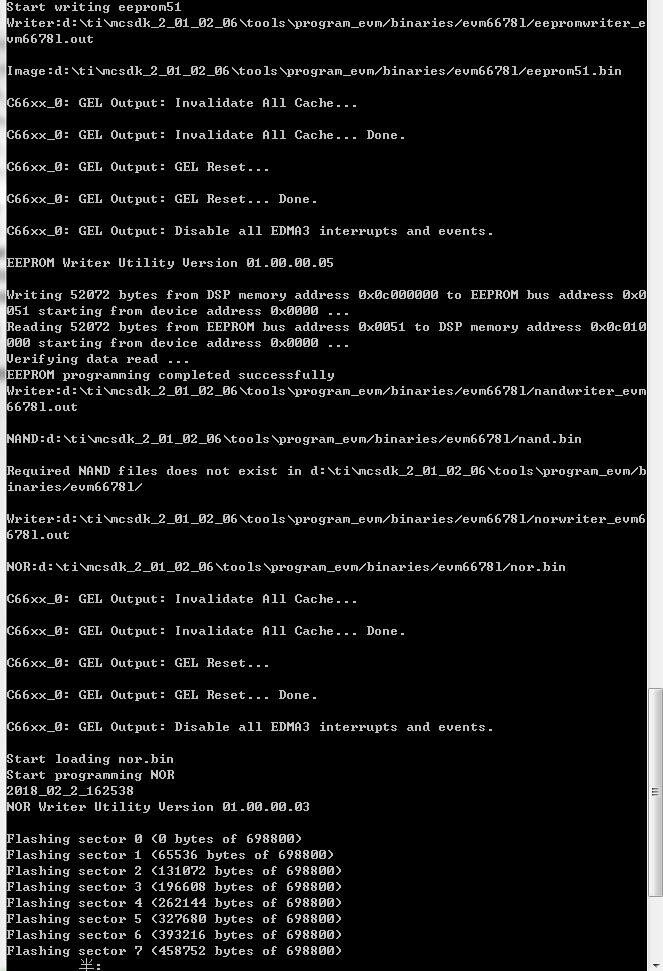

so i suspect that my IBL has some problem.after that,i find "get the EVM back to factory default state"in BIOS MCSDK user guide page 117,and i follow the procedure and finally get the output information which indicated that i was done successfully(i think it is)

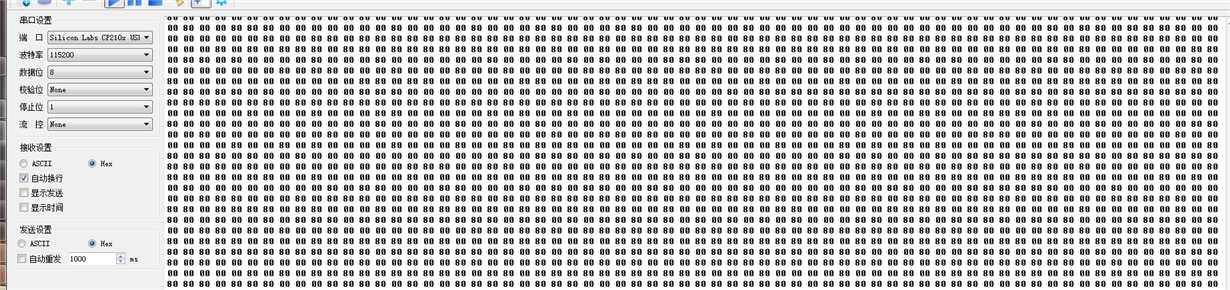

but when i do the Varification as shown in page 14 of program_evm_userguide,the UART didn't print the information described in the doc,but it print some garbled characters like this:

i didn't know what's going on,and when i do the Verifying NOR it also didn't print information like the doc mentioned.briefly,it seems like the IBL can't start up rightly.i hpoe someone can help me,thanks,sincerely!