Other Parts Discussed in Thread: AM4376

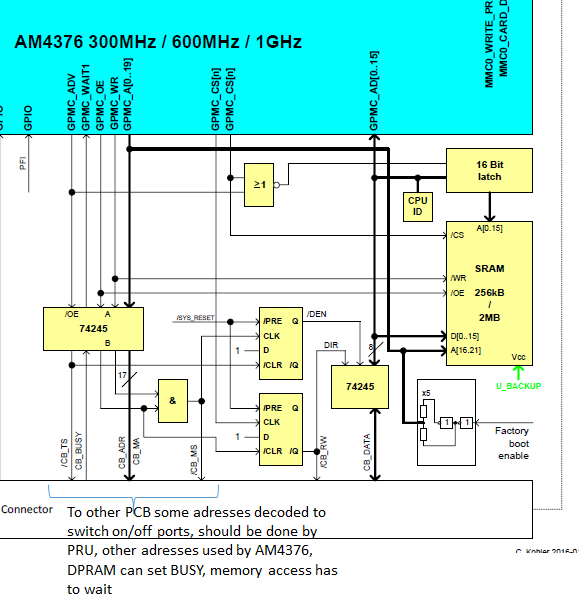

I need to access a memory mapped device through PRU. The main CPU also needs to access the same memory area, but not identical adresses. Will this be possible at all? Will the PRU wait when the memory is busy? It is a slow memory, 1 access needs about 100ns, so either core would have to wait while the other has access to the memory.