Other Parts Discussed in Thread: SN65HVS882

Tool/software: Linux

Hi,

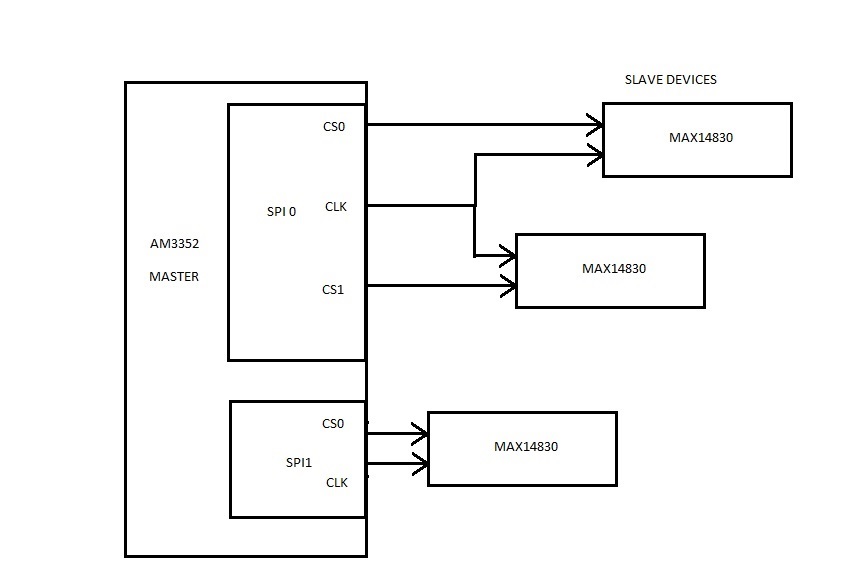

We have a custom board with AM3352 processor. we connected three MAX14830 (SPI to QUAD Uart IC). AM3352 is configured as MASTER . We are using ti-sdk only. Linux Version: linux-4.4.41+gitAUTOINC+f9f6f0db2d-gf9f6f0db2d, Diagramatic representation is given bellow of our design,

I Have configured the Pin Mux. Given Bellow for the reference,

spi1_pins: myspi1_pins_default {

pinctrl-single,pins = <

AM33XX_IOPAD(0x950, PIN_INPUT_PULLUP | MUX_MODE0 ) /* (A17) spi0_sclk.spi0_sclk */

AM33XX_IOPAD(0x954, PIN_INPUT_PULLUP | MUX_MODE0 ) /* (B17) spi0_d0.spi0_d0 */

AM33XX_IOPAD(0x958, PIN_INPUT_PULLUP | MUX_MODE0 ) /* (B16) spi0_d1.spi0_d1 */

AM33XX_IOPAD(0x95c, PIN_INPUT_PULLUP | MUX_MODE0 ) /* (A16) spi0_cs0.spi0_cs0 */

AM33XX_IOPAD(0x960, PIN_INPUT_PULLUP | MUX_MODE0 ) /* (C15) spi0_cs1.spi0_cs1 */

>;

};

spi2_pins: myspi2_pins_default {

pinctrl-single,pins = <

AM33XX_IOPAD(0x908, PIN_OUTPUT_PULLUP | MUX_MODE2 ) /* (H16) gmii1_col.spi1_sclk */

AM33XX_IOPAD(0x90c, PIN_OUTPUT_PULLUP | MUX_MODE2 ) /* (H17) gmii1_crs.spi1_d0 */

AM33XX_IOPAD(0x910, PIN_INPUT_PULLUP | MUX_MODE2 ) /* (J15) gmii1_rxer.spi1_d1 */

AM33XX_IOPAD(0x944, PIN_OUTPUT_PULLUP | MUX_MODE2 ) /* (H18) rmii1_refclk.spi1_cs0 */

AM33XX_IOPAD(0x964, PIN_OUTPUT_PULLUP | MUX_MODE2 ) /* (C18) eCAP0_in_PWM0_out.spi1_cs1 */

Changes has been made in the dts file

&spi0 {

#address-cells = <1>;

#size-cells = <0>;

pinctrl-names = "default";

pinctrl-0 = <&spi1_pins>;

cs-gpios = <&gpio0 5 0>, <&gpio0 6 0>;

ti,pindir-d0-out-d1-in = <1>;

spi-cpha;

spi-cpol;

status = "okay";

U6: max14830@0 {

compatible="maxim,max14830";

reg = <1>;

mode = <0>;

spi-max-frequency=<26000000>;

clocks=<&clk4m>;

clock-names="osc";

interrupt-parent=<&gpio3>;

interrupts=<15 8>;

gpio-controller;

#gpio-cells = <2>;

status = "okay";

};

};

&spi1 {

#address-cells = <1>;

#size-cells = <0>;

pinctrl-names = "default";

pinctrl-0 = <&spi2_pins>;

ti,pindir-d0-out-d1-in = <1>;

spi-cpha;

cs-gpios = <&gpio0 5 0>, <&gpio0 6 0>;

ti,pindir-d0-out-d1-in = <1>;

spi-cpha;

spi-cpol;

status = "okay";

U5: max14830@1 {

compatible = "maxim,max14830";

reg = <1>;

mode = <0>;

spi-max-frequency = <26000000>;

clocks = <&spi_uart_clk>;

clock-names = "osc";

//interrupt-parent = <&gpio3>;

//interrupts = <14 0x2>;

gpio-controller;

#gpio-cells = <2>;

};

U4: max14830@1 {

compatible = "maxim,max14830";

reg = <0>;

mode = <0>;

spi-max-frequency = <26000000>;

clocks = <&spi_uart_clk>;

clock-names = "osc";

//interrupt-parent = <&gpio3>;

//interrupts = <21 0x2>;

gpio-controller;

#gpio-cells = <2>;

};

};

Questions:

1. We are not getting the Clock and Chip select signal ?

2. Any changes has to be done in driver ?

3. Any changes has to be do in device tree ?

4. What can be the issue?