Tool/software: TI-RTOS

Dear

We use K2G_bf_rt in the processor_sdk_rtos_k2g_4_01_00_06 to do our project, we want use McASP 0 instead of McASP 1 as Rx .

So we make some changes on the programme, as follow :

#if 1

/* Added by HeWujun 2018.4.12, for K2G_M001_A6x_Platform */

/* Bind McASP0 for Rx */

status = mcaspBindDev(&hMcaspDevRx, CSL_MCASP_0, &mcaspRxParams);

if((status != MCASP_COMPLETED) || (hMcaspDevRx == NULL))

{

IFPRINT(cmb_write("mcaspBindDev for Rx Failed\n"));

IFPRINT(UART_printf("mcaspBindDev for Rx Failed\n"));

return (Cmb_EFAIL);

}

#else

/* Bind McASP1 for Rx */

status = mcaspBindDev(&hMcaspDevRx, CSL_MCASP_1, &mcaspRxParams);

if((status != MCASP_COMPLETED) || (hMcaspDevRx == NULL))

{

IFPRINT(cmb_write("mcaspBindDev for Rx Failed\n"));

IFPRINT(UART_printf("mcaspBindDev for Rx Failed\n"));

return (Cmb_EFAIL);

}

#endif

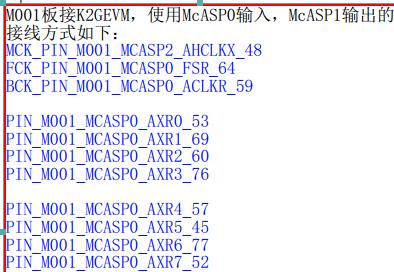

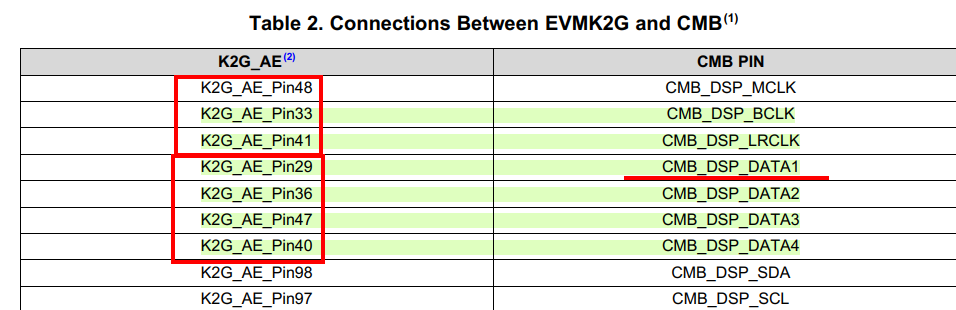

On hardware. we made some changes on connections,as follows:

instead of TI provide infomation:

But when test . there are some errors . Log from console is as follow:

[C66xx]

******************************************

Audio Preprocessing Demo22

******************************************

This Demo Takes the Audio Input from 8 Mics from CMB

Runs the BF+ASNR+MSS+DRC Signal Processing Chain on Mic1 through Mic7

The Processed Audio Output will be Sent to Left Channels of K2G EVM On-Board Line-Out

The Mic8 will be Sent to Right Channels of K2G EVM On-Board Line-Out

Please Plug a Headphone to K2G EVM On-Board Line-Out

******************************************

******************************************

cmb_cmb_pcm186xReset(), IIC 0 : addr = 0x94

K2G_M001_platform ReSet U2

cmb_cmb_pcm186xReset(), IIC 0 : addr = 0x96

K2G_M001_platform ReSet U3

K2G_M001_platform Set U2 in Master Mode

******************************************

******************************************

Audio I2C0 0x96 U3 Configuration !

addr = 0x96 page = -1

in Writing Register = 0x0 data = 0x0

in Writing Register = 0x6 data = 0x41

in Writing Register = 0x7 data = 0x41

in Writing Register = 0x8 data = 0x44

in Writing Register = 0x9 data = 0x44

in Writing Register = 0xb data = 0x44

in Writing Register = 0x10 data = 0x0

in Writing Register = 0x11 data = 0x50

in Writing Register = 0x12 data = 0x0

in Writing Register = 0x13 data = 0x40

in Writing Register = 0x20 data = 0x1

cmb_pcm186xAdcInit() : In Page=0x0

cmb_AudioAdcInit_I2C0()。。。

cmb_AudioAdcSetGain_I2C0()。。。

..........................

cmb_AudioAdcConfigIntr_I2C0()...

DATA6 DATA7 Test !

******************************************

******************************************

Audio I2C0 0x94 U2 Configuration !

addr = 0x94 page = 0

in Writing Register = 0x0 data = 0x0

in Writing Register = 0x6 data = 0x41

in Writing Register = 0x7 data = 0x41

in Writing Register = 0x8 data = 0x44

in Writing Register = 0x9 data = 0x44

in Writing Register = 0xb data = 0x44

in Writing Register = 0x10 data = 0x3

in Writing Register = 0x11 data = 0x50

in Writing Register = 0x12 data = 0x4

in Writing Register = 0x13 data = 0x40

cmb_pcm186xAdcInit() : In Page=0x0

cmb_AudioAdcInit_I2C0()。。。

cmb_AudioAdcSetGain_I2C0()。。。

..........................

cmb_AudioAdcConfigIntr_I2C0()...

DATA0 DATA1 Test !

McASP Configuration Failed!

Audio DC Analog Interface Test Completed!

A0=0x0 A1=0x1

A2=0x1 A3=0xc0e0108

A4=0x1 A5=0x42a

A6=0x87d084 A7=0x1

A8=0x87ce38 A9=0x87ce40

A10=0x10 A11=0x0

A12=0x8fe5b0 A13=0x0

A14=0x1 A15=0x8fff00

A16=0x5a1e797b A17=0x31

A18=0x0 A19=0x3e034900

A20=0x10 A21=0x0

A22=0x0 A23=0x20

A24=0x0 A25=0x20

A26=0x8fff00 A27=0x876cdb

A28=0x87d0b8 A29=0x8215d0

A30=0x82bc24 A31=0x1a

B0=0x1 B1=0x3

B2=0x0 B3=0x82d688

B4=0x87cff8 B5=0x87d0c0

B6=0x1 B7=0x87897c

B8=0x8fe5b0 B9=0x0

B10=0x876d58 B11=0x872c94

B12=0x82a5bc B13=0x5a1e797b

B14=0x87d600 B15=0x87d0d8

B16=0x0 B17=0x87d040

B18=0x0 B19=0x87d040

B20=0xffffffff B21=0xffffffff

B22=0xfffffff7 B23=0x0

B24=0x66666666 B25=0x30666666

B26=0x800 B27=0xfffff7ff

B28=0xffffffe6 B29=0x876e14

B30=0x87cff8 B31=0x0

NTSR=0x1000a

ITSR=0x82d634

IRP=0xa

SSR=0x2d

AMR=0x8fe5b0

RILC=0xc

ILC=0x87d08c

Exception at 0x40b6d190

EFR=0x2 NRP=0x40b6d190

Internal exception: IERR=0x1

Instruction fetch exception

ti.sysbios.family.c64p.Exception: line 256: E_exceptionMax: pc = 0x00000000, sp = 0x00000000.

xdc.runtime.Error.raise: terminating execution

We can fix the error from the function :

/* Create McASP channel for Rx */

status = mcaspCreateChan(&hMcaspRxChan, hMcaspDevRx,

MCASP_INPUT,

&mcaspRxChanParam,

mcaspAppCallback, &rxChanMode);

if((status != MCASP_COMPLETED) || (hMcaspRxChan == NULL))

{

IFPRINT(cmb_write("mcaspCreateChan for Rx Failed\n"));

IFPRINT(UART_printf("mcaspCreateChan for Rx Failed\n"));

return (Cmb_EFAIL);

}

But I do not know how to make them correct .Can you give me some suggestion ? Thank you for your help .

Wujun He