Other Parts Discussed in Thread: TCI6638K2K, TCI6636K2H, 66AK2H12

Tool/software: Code Composer Studio

Hi

We have designed customized board using 66AK2H14. We are using CCSV7 and ti-processor-sdk-rtos-k2hk-evm-04.01.00.06.

we are using TI XDS 110 debug probe .

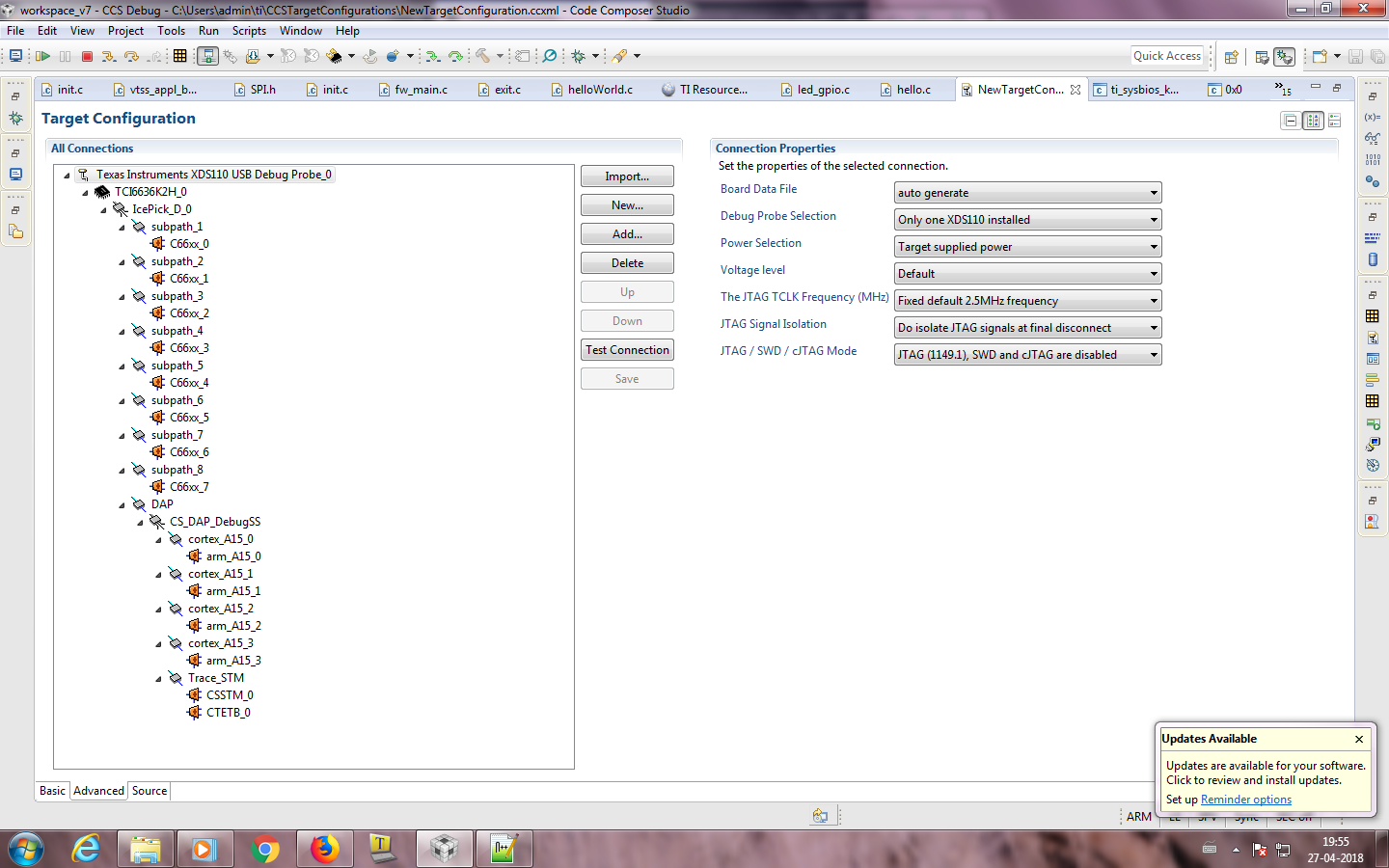

this is our target configuration.

and we are using C:\ti\ccsv7\ccs_base\emulation\boards\xtcievmk2x\gel gel files .

gel file is loaded successfully with below log

arm_A15_0: GEL Output: Disabling MMU

arm_A15_0: GEL Output: Disabling Caches

arm_A15_0: GEL Output: Invalidate Instruction Caches

arm_A15_0: GEL Output: Enabling non-secure access to cp10 and cp11

arm_A15_0: GEL Output: Enabled non-secure access to cp10 and cp11

arm_A15_0: GEL Output: Enabling SMP bit in ACTLR

arm_A15_0: GEL Output: Enabled SMP bit in ACTLR

arm_A15_0: GEL Output: Entering NonSecure Mode

arm_A15_0: GEL Output: Entered NonSecure Mode

arm_A15_0: GEL Output: Disabling MMU

arm_A15_0: GEL Output: Disabling Caches

arm_A15_0: GEL Output: Invalidate Instruction Caches

arm_A15_0: GEL Output:

Connecting Target...

arm_A15_0: GEL Output: Disabling MMU

arm_A15_0: GEL Output: Disabling Caches

arm_A15_0: GEL Output: Invalidate Instruction Caches

arm_A15_0: GEL Output: Enabling non-secure access to cp10 and cp11

arm_A15_0: GEL Output: Enabled non-secure access to cp10 and cp11

arm_A15_0: GEL Output: Enabling SMP bit in ACTLR

arm_A15_0: GEL Output: Enabled SMP bit in ACTLR

arm_A15_0: GEL Output: Entering NonSecure Mode

arm_A15_0: GEL Output: Entered NonSecure Mode

arm_A15_0: GEL Output: Disabling MMU

arm_A15_0: GEL Output: Disabling Caches

arm_A15_0: GEL Output: Invalidate Instruction Caches

arm_A15_0: GEL Output: TCI6638K2K GEL file Ver is 1.70000005

arm_A15_0: GEL Output: Disabling MMU

arm_A15_0: GEL Output: Disabling Caches

arm_A15_0: GEL Output: Invalidate Instruction Caches

arm_A15_0: GEL Output: Enabling non-secure access to cp10 and cp11

arm_A15_0: GEL Output: Enabled non-secure access to cp10 and cp11

arm_A15_0: GEL Output: Enabling SMP bit in ACTLR

arm_A15_0: GEL Output: Enabled SMP bit in ACTLR

arm_A15_0: GEL Output: Entering NonSecure Mode

arm_A15_0: GEL Output: Entered NonSecure Mode

arm_A15_0: GEL Output: Disabling MMU

arm_A15_0: GEL Output: Disabling Caches

arm_A15_0: GEL Output: Invalidate Instruction Caches

arm_A15_0: GEL Output: Detected PLL bypass enabled: SECCTL[BYPASS] = 0x00800000

arm_A15_0: GEL Output: (2a) MAINPLLCTL1 = 0x00000040

arm_A15_0: GEL Output: (2b) PLLCTL = 0x00000048

arm_A15_0: GEL Output: (2c) PLLCTL = 0x00000048

arm_A15_0: GEL Output: (2d) Delay...

arm_A15_0: GEL Output: (2e) SECCTL = 0x00810000

arm_A15_0: GEL Output: (2f) PLLCTL = 0x0000004A

arm_A15_0: GEL Output: (2g) Delay...

arm_A15_0: GEL Output: (2h) PLLCTL = 0x00000048

arm_A15_0: GEL Output: (4)PLLM[PLLM] = 0x0000000F

arm_A15_0: GEL Output: MAINPLLCTL0 = 0x05000000

arm_A15_0: GEL Output: (5) MAINPLLCTL0 = 0x07000000

arm_A15_0: GEL Output: (5) MAINPLLCTL1 = 0x00000040

arm_A15_0: GEL Output: (6) MAINPLLCTL0 = 0x07000000

arm_A15_0: GEL Output: (7) SECCTL = 0x00890000

arm_A15_0: GEL Output: (8a) Delay...

arm_A15_0: GEL Output: PLL1_DIV3 = 0x00008002

arm_A15_0: GEL Output: PLL1_DIV4 = 0x00008004

arm_A15_0: GEL Output: PLL1_DIV7 = 0x00000000

arm_A15_0: GEL Output: (8d/e) Delay...

arm_A15_0: GEL Output: (10) Delay...

arm_A15_0: GEL Output: (12) Delay...

arm_A15_0: GEL Output: (13) SECCTL = 0x00090000

arm_A15_0: GEL Output: (Delay...

arm_A15_0: GEL Output: (Delay...

arm_A15_0: GEL Output: (14) PLLCTL = 0x00000041

arm_A15_0: GEL Output: PLL has been configured (CLKIN * PLLM / PLLD / PLLOD = PLLOUT):

arm_A15_0: GEL Output: PLL has been configured (122.879997 MHz * 16 / 1 / 2 = 983.039978 MHz)

arm_A15_0: GEL Output: Switching on ARM Core 0

arm_A15_0: GEL Output: Switching on ARM Core 1

arm_A15_0: GEL Output: Switching on ARM Core 2

arm_A15_0: GEL Output: Switching on ARM Core 3

arm_A15_0: GEL Output: ARM PLL has been configured (125.0 MHz * 16 / 2 = 1000.0 MHz)

arm_A15_0: GEL Output: Power on all PSC modules and DSP domains...

arm_A15_0: GEL Output: Set_PSC_State... Timeout Error #03 pd=2, md=9!

arm_A15_0: GEL Output: Set_PSC_State... Timeout Error #03 pd=17, md=25!

arm_A15_0: GEL Output: Set_PSC_State... Timeout Error #03 pd=17, md=26!

arm_A15_0: GEL Output: Set_PSC_State... Timeout Error #03 pd=18, md=27!

arm_A15_0: GEL Output: Set_PSC_State... Timeout Error #03 pd=19, md=28!

arm_A15_0: GEL Output: Set_PSC_State... Timeout Error #03 pd=19, md=29!

arm_A15_0: GEL Output: Set_PSC_State... Timeout Error #03 pd=20, md=30!

arm_A15_0: GEL Output: Set_PSC_State... Timeout Error #03 pd=20, md=31!

arm_A15_0: GEL Output: Set_PSC_State... Timeout Error #03 pd=20, md=32!

arm_A15_0: GEL Output: Set_PSC_State... Timeout Error #03 pd=20, md=33!

arm_A15_0: GEL Output: Set_PSC_State... Timeout Error #03 pd=21, md=34!

arm_A15_0: GEL Output: Set_PSC_State... Timeout Error #03 pd=22, md=35!

arm_A15_0: GEL Output: Set_PSC_State... Timeout Error #03 pd=22, md=36!

arm_A15_0: GEL Output: Set_PSC_State... Timeout Error #03 pd=23, md=37!

arm_A15_0: GEL Output: Set_PSC_State... Timeout Error #03 pd=23, md=38!

arm_A15_0: GEL Output: Set_PSC_State... Timeout Error #03 pd=24, md=39!

arm_A15_0: GEL Output: Set_PSC_State... Timeout Error #03 pd=24, md=40!

arm_A15_0: GEL Output: Set_PSC_State... Timeout Error #03 pd=24, md=41!

arm_A15_0: GEL Output: Set_PSC_State... Timeout Error #03 pd=24, md=42!

arm_A15_0: GEL Output: Set_PSC_State... Timeout Error #03 pd=25, md=43!

arm_A15_0: GEL Output: Set_PSC_State... Timeout Error #03 pd=25, md=44!

arm_A15_0: GEL Output: Set_PSC_State... Timeout Error #03 pd=25, md=45!

arm_A15_0: GEL Output: Set_PSC_State... Timeout Error #03 pd=25, md=46!

arm_A15_0: GEL Output: Set_PSC_State... Timeout Error #03 pd=26, md=47!

arm_A15_0: GEL Output: Set_PSC_State... Timeout Error #03 pd=27, md=48!

arm_A15_0: GEL Output: Power on all PSC modules and DSP domains... Done.

arm_A15_0: GEL Output: WARNING: SYSCLK is the input to the PA PLL.

arm_A15_0: GEL Output: Completed PA PLL Setup

arm_A15_0: GEL Output: PAPLLCTL0 - before: 0x0x098804C0 after: 0x0x09080500

arm_A15_0: GEL Output: PAPLLCTL1 - before: 0x0x00000040 after: 0x0x00002040

arm_A15_0: GEL Output: DDR begin

arm_A15_0: GEL Output: XMC setup complete.

arm_A15_0: GEL Output: DDR3 PLL (PLL2) Setup ...

arm_A15_0: GEL Output: DDR3 PLL Setup complete, DDR3A clock now running at 666 MHz.

arm_A15_0: GEL Output: DDR3A initialization complete

arm_A15_0: GEL Output: DDR done

arm_A15_0: GEL Output: Entering A15 non secure mode ..

arm_A15_0: GEL Output: Disabling MMU

arm_A15_0: GEL Output: Disabling Caches

arm_A15_0: GEL Output: Invalidate Instruction Caches

arm_A15_0: GEL Output: Enabling non-secure access to cp10 and cp11

arm_A15_0: GEL Output: Enabled non-secure access to cp10 and cp11

arm_A15_0: GEL Output: Enabling SMP bit in ACTLR

arm_A15_0: GEL Output: Enabled SMP bit in ACTLR

arm_A15_0: GEL Output: Entering NonSecure Mode

arm_A15_0: GEL Output: Entered NonSecure Mode

arm_A15_0: GEL Output: Disabling MMU

arm_A15_0: GEL Output: Disabling Caches

arm_A15_0: GEL Output: Invalidate Instruction Caches

arm_A15_0: GEL Output: A15 non secure mode entered

but when we try to load the program to arm core0 it is giving following error.

arm_A15_0: Trouble Reading Memory Block at 0x80000000 on Page 0 of Length 0x4: (Error -1205 @ 0x80000000) Device memory bus has an error and may be hung. Verify that the memory address is in valid memory. If error persists, confirm configuration, power-cycle board, and/or try more reliable JTAG settings (e.g. lower TCLK). (Emulation package 6.0.628.3)

arm_A15_0: File Loader: Verification failed: Target failed to read 0x80000000

arm_A15_0: GEL: File: C:\Users\admin\workspace_v7\I2C_BasicExample_K2H_armTestProject\Debug\I2C_BasicExample_K2H_armTestProject.out: Load failed.

arm_A15_0: Unable to terminate memory download: NULL buffer pointer at 0x3aa4

arm_A15_0: Trouble Reading Register REG_SYSTEM_TARGET_CONFIG: (Error -1141 @ 0x3D58) Device is not responding to the request. Reset the device, and retry the operation. If error persists, confirm configuration, power-cycle the board, and/or try more reliable JTAG settings (e.g. lower TCLK). (Emulation package 6.0.628.3)

arm_A15_0: Trouble Reading Register REG_SYSTEM_MMU_CONFIG: (Error -1141 @ 0x3D58) Device is not responding to the request. Reset the device, and retry the operation. If error persists, confirm configuration, power-cycle the board, and/or try more reliable JTAG settings (e.g. lower TCLK). (Emulation package 6.0.628.3)

we are using 4GB DDR3 64 bit.

when we try to read/write from DDR3 using GEL ddr3A_memory_test() it is giving below errors.

arm_A15_0: Trouble Writing Memory Block at 0x80000000 on Page 0 of Length 0x4: (Error -1141 @ 0x3D58) Device is not responding to the request. Reset the device, and retry the operation. If error persists, confirm configuration, power-cycle the board, and/or try more reliable JTAG settings (e.g. lower TCLK). (Emulation package 6.0.628.3)

arm_A15_0: GEL: Error while executing OnTargetConnect(): Target failed to write 0x80000000

at *(index)=index [xtcievmk2x_arm.gel:1499]

at ddr3A_memory_test() [xtcievmk2x_arm.gel:689]

at Global_Default_Setup_Silent() [xtcievmk2x_arm.gel:597]

at OnTargetConnect()

arm_A15_0: Trouble Reading Register REG_SYSTEM_TARGET_CONFIG: (Error -1141 @ 0x3D58) Device is not responding to the request. Reset the device, and retry the operation. If error persists, confirm configuration, power-cycle the board, and/or try more reliable JTAG settings (e.g. lower TCLK). (Emulation package 6.0.628.3)

arm_A15_0: Trouble Reading Register REG_SYSTEM_MMU_CONFIG: (Error -1141 @ 0x3D58) Device is not responding to the request. Reset the device, and retry the operation. If error persists, confirm configuration, power-cycle the board, and/or try more reliable JTAG settings (e.g. lower TCLK). (Emulation package 6.0.628.3)

arm_A15_0: Trouble Reading Register REG_SYSTEM_MMU_STATUS: (Error -1141 @ 0x3D58) Device is not responding to the request. Reset the device, and retry the operation. If error persists, confirm configuration, power-cycle the board, and/or try more reliable JTAG settings (e.g. lower TCLK). (Emulation package 6.0.628.3)

arm_A15_0: Trouble Reading Register REG_SYSTEM_MMU_STATUS: (Error -1141 @ 0x3D58) Device is not responding to the request. Reset the device, and retry the operation. If error persists, confirm configuration, power-cycle the board, and/or try more reliable JTAG settings (e.g. lower TCLK). (Emulation package 6.0.628.3)

Q1. Do we need to change anything in the GEL file?

Q2. Whether we have to change this 0x80000000 to some other value.

Please help me to solve these errors.

Thank you,

Mahima Shanbag